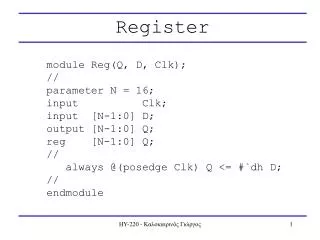

Register

Register. Serial In - Serial Out Shift Registers. เข้าอนุกรม ออกอนุกรม จะเลื่อนข้อมูลตามสัญญาณ clock. ปัญหาข้อมูลโดนทำลาย. เกิดจากการเลื่อนข้อมูล ตัวรับอาจจะรับข้อมูลไม่ทัน เมื่อเราเคลียร์ข้อมูลด้วย 0000. การแก้ปัญหา. การแก้ปัญหา สามารถเลือก Read, Write ได้.

Register

E N D

Presentation Transcript

Serial In - Serial Out Shift Registers • เข้าอนุกรม ออกอนุกรม • จะเลื่อนข้อมูลตามสัญญาณ clock

ปัญหาข้อมูลโดนทำลาย • เกิดจากการเลื่อนข้อมูล • ตัวรับอาจจะรับข้อมูลไม่ทัน เมื่อเราเคลียร์ข้อมูลด้วย 0000

การแก้ปัญหา • การแก้ปัญหา • สามารถเลือก Read, Write ได้ 0->ป้อนกลับ, 1->รับอินพุท

Serial In - Parallel Out Shift Registers • เข้าอนุกรม ออกขนาน

Parallel In - Serial Out Shift Registers • เข้าขนาน ออกอนุกรม

Parallel In - Parallel Out Shift Registers • เข้าขนาน ออกขนาน

Bidirectional Shift Registers • สองทาง

Shift Register Counters • ตัวนับ Ring Counter RESTART

Shift Register Counters • ตัวนับ Johnson Counter

ROM • Read Only Memory • หน่วยตวามจำที่อ่านได้เพียงอย่างเดียว เขียนทับไม่ได้ • ถูกกำหนดข้อมูลมาจากผู้ผลิตแล้ว • ROM ที่เขียนทับได้ • EPROM สามารถลบข้อมูลได้ด้วยรังสี UV • EEPROM สามารถลบข้อมูลได้ด้วยไฟฟ้า • Flash สามารถลบข้อมูลได้ด้วยไฟฟ้า เขียนได้หลายครั้ง

ROM ใน PC (8088) ROM Address bus Data bus A0-A10 O0-O10 CE OE CE = chip enable OE = output enable =Trigger ที่ขอบขาลง Control bus

ROM ใน PC (8088) Memory Interface 8088/8086 A0-A10 ROM Chip Address bus A0-A10 CS MEMR CE OE Control bus O0-O10 Data bus D0-D10

Time Diagram ของ EPROM กับ CPU Address CE OE Output High-Z

RAM ใน 8088 • สมมติว่า มี 4 Bank • Bank ละ 8K , 1 แอดเดรส = 8 บิท (8K 8) 213 = 8192= 8K 8 บิท . . . เราสามารถใช้เทคนิคให้เข้าถึง RAM ได้ถึง 16K จำนวน 2Bank รวมเป็น 32K 8 K โดยใช้ 14 บิท (A0 -A13 ) และเพิ่ม 1 – 2 Decoder มา 1 ตัว

Low Byte Bank 0 A0-A12 WE CE OE A0 A1 .. A12 13 A0-A10 CPU & SRAM ใน 8088 WE CE OE 16 13 High Byte Bank 0 SRAM 4 Bank Bank ละ 8K 8 D0 D1 .. D15 13 Low Byte Bank 1 A0-A12 WE CE 0 -> CS0 = 0, CS1 = 1 1 -> CS1 = 0 , CS0 = 1 13 16 OE MEMW CS0 A0-A12 A13 Address Decoder CS0 CS1 WE CS1 High Byte Bank 1 CE MEMR OE

สมมติว่าจะ READ ข้อมูลที่ Bank 0 A0 -A12 A13 MEMR D0 -D12

สมมติว่าจะ READ ข้อมูลที่ Bank 1 A0 -A12 A13 MEMR D0 -D12

สมมติว่าจะ WRITE ข้อมูลที่ Bank 0 A0 -A12 A13 MEMW D0 -D12