Verilog Modules for Register and Flip-Flop Designs

This documentation showcases various Verilog modules designed for digital circuits including registers, flip-flops, multiplexers, and counters. Key modules include standard registers with reset capabilities, loadable registers, T flip-flops, positive edge detectors, and a series of multiplexers for efficient data selection. Additional functionalities such as parallel-to-serial and serial-to-parallel conversions, as well as priority encoders and decoders, are also presented. These tools can greatly enhance digital design workflows and enable effective testing and implementation.

Verilog Modules for Register and Flip-Flop Designs

E N D

Presentation Transcript

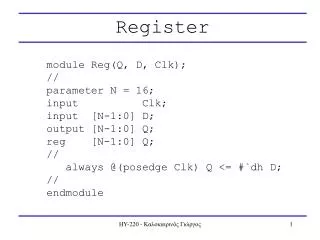

Register module Reg(Q, D, Clk); // parameter N = 16; input Clk; input [N-1:0] D; output [N-1:0] Q; reg [N-1:0] Q; // always @(posedge Clk) Q <= #`dh D; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Register Reset_ module RegRst(Q, D, Reset_, Clk); // parameter N = 16; // input Reset_, Clk; input [N-1:0] D; output [N-1:0] Q; reg [N-1:0] Q; // always @(posedge Clk or negedge Reset_) begin if (!Reset_) Q <= 0; else Q <= #`dh D; end endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Register Ld module RegLd(Q, D, Ld, Clk); // parameter N = 16; input Ld, Clk; input [N-1:0] D; output [N-1:0] Q; reg [N-1:0] Q; // always @(posedge Clk) if (Ld) Q <= #`dh D; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Set Clear flip-flop Strong Clear module sCff(Out, Set, Clear, Clk); // output Out; input Set, Clear, Clk; // reg Out; always @(posedge Clk) Out <= #`dh (Out | Set) & ~Clear; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Set Clear flip-flop Strong Set module Scff(Out, Set, Clear, Clk); // output Out; input Set, Clear, Clk; // reg Out; always @(posedge Clk) Out <= #`dh Set | (Out & ~Clear); // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

T Flip Flop module Tff(Out, Toggle, Clk); // output Out; input Toggle, Clk; // reg Out; always @(posedge Clk) if(Toggle) Out <= #`dh ~Out; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Positive Edge Detector module PosEdgDet(Out, In, Clk); // input In, Clk; output Out; // reg Tmp; always @(posedge Clk) Tmp <= #`dh In; wire Out = ~Tmp & In; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Mux2 module mux2(Out, In1, In0, Sel); // parameter N = 16; output [N-1:0] Out; input [N-1:0] In1, In0; input Sel; // wire [N-1:0] Out = Sel ? In1 : In0; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Mux4 module mux4(Out, In3, In2, In1, In0, Sel); // parameter N = 32; input [ 1:0] Sel; input [N-1:0] In3, In2, In1, In0; output [N-1:0] Out; reg [N-1:0] Out; // always @(In0 or In1 or In2 or In3 or Sel) begin case ( Sel ) // synopsys infer_mux 2'b00 : Out = In0; 2'b01 : Out = In1; 2'b10 : Out = In2; 2'b11 : Out = In3; endcase end endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Tris module Tris(TrisOut, TrisIn, TrisOen_); // parameter N = 32; input [N-1:0] TrisIn; input TrisOen_; output [N-1:0] TrisOut; // wire [N-1:0] TrisOut = ~TrisOen ? TrisIn : ‘bz; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Mux4t1 RegLd Tris module MuxRegTris(Out, In0, In1, In2, In3, Select, Ld, TrisEn, Clk); // parameter N = 32; input Ld, TrisEn, Clk; input [ 1:0] Select; input [N-1:0] In0, In1, In2, In3; output [N-1:0] Out; reg [N-1:0] MuxReg; always @(posedge Clk) begin if(Ld) begin case(Select) 0 : MuxReg = In0; 1 : MuxReg = In1; 2 : MuxReg = In2; 3 : MuxReg = In3; endcase end end wire [N-1:0] Out = TrisEn ? MuxReg : 'bz; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Up Counter Divider module Cnt(Out, Zero, En, Clear, Clk); parameter N = 32; parameter MaxCnt = 9; input En, Clear, Clk; output Zero; output [N-1:0] Out; reg [N-1:0] Out; reg Zero; always @(posedge Clk) begin if(Clear) Out <= #`dh 0; else if(En) begin if(Out==MaxCnt) begin Out <= #`dh 0; Zero <= #`dh 1; end else begin Out <= #`dh Out + 1; Zero <= #`dh 0; end end end endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Parallel to Serial Shift Register module P2Sreg(Out, In, Ld, Shift, Clk, Reset_); parameter N = 32; input Ld, Shift, Clk, Reset_; input [N-1:0] In; output Out; reg [N-1:0] TmpVal; // always @(posedge Clk or negedge Reset_) begin if (~Reset_) TmpVal = #`dh 0; else begin if (Ld) TmpVal = #`dh In; else if(Shift) TmpVal = #`dh TmpVal>>1; end end wire Out = TmpVal[0]; endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Serial to Parallel Nbit Shift Register module S2Preg(Out, In, Shift, Clear, Clk); parameter N = 32; input In, Shift, Clear, Clk; output [N-1:0] Out; reg [N-1:0] Out; // wire [N-1:0] Tmp = {Out[N-2:0],In}; always @(posedge Clk) begin if(Clear) Out = #`dh 0; else if(Shift) Out = #`dh Tmp; end // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Priority Enforcer and Encoder ModulePriority is left <- right (MS) module PriorEnf(In, Out, OneDetected); parameter N = 8; input [N-1:0] In; output [N-1:0] Out; output OneDetected; reg [N-1:0] Out; reg OneDetected; integer i; // Temporary registers reg DetectNot; // Temporary registers always @(In) begin DetectNot=1; for (i=0; i<N; i=i+1) if (In[i] & DetectNot) begin Out[i]=1; DetectNot=0; end else Out[i]=0; OneDetected= !DetectNot; end endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

3 to 8 Decoder Module module Dec(In, Out); input [2:0] In; output [7:0] Out; reg [7:0] Out; integer i; reg [7:0] tmp; // always @(In) begin tmp = 0; for (i=0; i<8; i=i+1) if (In==i) tmp[i]=1; Out = tmp; end // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Latch module Latch(In, Out, Ld); // parameter N = 16; // input [N-1:0] In; input Ld; output [N-1:0] Out; // reg [N-1:0] Out; // always @(In or Ld) if(Ld) Out = #`dh In; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (1/5) module fsmJ(ReceiveSt, ErrorSt, Start, Stop, Error, Clk, Reset_); // input Start, Stop, Error, Clk, Reset_; output ReceiveSt, ErrorSt; // parameter [1:0] IdleState = 0, ReceiveState = 1, ErrorState = 2; // reg [1:0] FSMstate, nxtFSMstate; reg ReceiveSt, ErrorSt, nxtReceiveSt, nxtErrorSt; // always @(FSMstate or Start or Stop or Error) begin // case(FSMstate) ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (2/5) IdleState: begin if(Error) begin nxtFSMstate <= ErrorState; nxtReceiveSt <= 0; nxtErrorSt <= 1; end else begin if(Start) begin nxtFSMstate <= ReceiveState; nxtReceiveSt <= 1; nxtErrorSt <= 0; end else begin nxtFSMstate <= IdleState; nxtReceiveSt <= 0; nxtErrorSt <= 0; end end end ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (3/5) ReceiveState: begin if(Error) begin nxtFSMstate <= ErrorState; nxtReceiveSt <= 0; nxtErrorSt <= 1; end else begin if(Stop) begin nxtFSMstate <= IdleState; nxtReceiveSt <= 0; nxtErrorSt <= 0; end else begin nxtFSMstate <= ReceiveState; nxtReceiveSt <= 1; nxtErrorSt <= 0; end end end ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (4/5) ErrorState : begin nxtFSMstate <= IdleState; nxtReceiveSt <= 0; nxtErrorSt <= 0; end // default : begin nxtFSMstate <= IdleState; nxtReceiveSt <= 0; nxtErrorSt <= 0; end // endcase end ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (5/5) always @(posedge Clk) begin if (~Reset_) begin FSMstate <= #`dh IdleState; ReceiveSt <= #`dh 0; ErrorSt <= #`dh 0; end else begin FSMstate <= #`dh nxtFSMstate; ReceiveSt <= #`dh nxtReceiveSt; ErrorSt <= #`dh nxtErrorSt; end end // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (1/3) module fsmS(ReceiveSt, ErrorSt, Start, Stop, Error, Clk, Reset_); // input Start, Stop, Error, Clk, Reset_; output ReceiveSt, ErrorSt; // parameter [1:0] IdleState = 0, ReceiveState = 1, ErrorState = 2; // reg [1:0] FSMstate, nxtFSMstate; // always @(FSMstate or Start or Stop or Error) begin // case(FSMstate) ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (2/3) IdleState: begin if(Error) nxtFSMstate <= ErrorState; else begin if(Start) nxtFSMstate <= ReceiveState; else nxtFSMstate <= IdleState; end end // ReceiveState: begin if(Error) nxtFSMstate <= ErrorState; else begin if(Stop) nxtFSMstate <= IdleState; else nxtFSMstate <= ReceiveState; end end ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM (3/3) // ErrorState : nxtFSMstate <= IdleState; // default : nxtFSMstate <= IdleState; // endcase end // always @(posedge Clk) begin if (~Reset_) FSMstate <= #`dh IdleState; else FSMstate <= #`dh nxtFSMstate; end // wire ReceiveSt = FSMstate[0]; wire ErrorSt = FSMstate[1]; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM 1/4 module fsmM(ReceiveSt, ErrorSt, Start, Stop, Error, Clk, Reset_); // input Start, Stop, Error, Clk, Reset_; output ReceiveSt, ErrorSt; // parameter [1:0] IdleState = 0, ReceiveState = 1, ErrorState = 3; // reg [1:0] FSMstate, nxtFSMstate; // always @(FSMstate or Start or Stop or Error) begin // case(FSMstate) ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM 2/4 IdleState: begin if(Error) nxtFSMstate <= ErrorState; else begin if(Start) nxtFSMstate <= ReceiveState; else nxtFSMstate <= IdleState; end end // ReceiveState: begin if(Error) nxtFSMstate <= ErrorState; else begin if(Stop) nxtFSMstate <= IdleState; else nxtFSMstate <= ReceiveState; end end ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM 3/4 // ErrorState : nxtFSMstate <= IdleState; // default : nxtFSMstate <= IdleState; // endcase end // always @(posedge Clk) begin if (~Reset_) FSMstate <= #`dh IdleState; else FSMstate <= #`dh nxtFSMstate; end // ΗΥ-220 - Καλοκαιρινός Γιώργος

FSM 4/4 reg ReceiveSt; wire SetRcvSt = (FSMstate==IdleState)&Start; wire ClrRcvSt = (FSMstate==ReceiveState)&(Error|Stop); // always @(posedge Clk) begin if (~Reset_) ReceiveSt <= 0; else ReceiveSt <= (ReceiveSt | SetRcvSt)&~ClrRcvSt; end // wire ErrorSt = FSMstate[1]; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Single Port SRAM module SPRAM(Addr, Data, Write_, Oen_, Cs_); // parameter ADDR_WIDTH = 8, DATA_WIDTH = 8; // input Write_, Oen_, Cs_; input [ADDR_WIDTH-1:0] Addr; inout [DATA_WIDTH-1:0] Data; // reg [DATA_WIDTH-1:0] mem[(1 << ADDR_WIDTH)-1:0]; reg [DATA_WIDTH-1:0] DataTmp; // always @(Write_ or Oen_ or Addr or Cs_ or Data) begin DataTmp = ((!Oen_ & Write_ & !Cs_) ? mem[Addr] : 'bz); if (!Write_& !Cs_) mem[Addr] = Data; end wire [DATA_WIDTH-1:0] Data = DataTmp; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Dual Port SRAM module DPSRAM(WAddr, RAddr, DataIn, DataOut, Write_, Read_); // parameter ADDR_WIDTH = 8, DATA_WIDTH = 8; input Write_, Read_; input [ADDR_WIDTH-1:0] WAddr, RAddr; input [DATA_WIDTH-1:0] DataIn; output [DATA_WIDTH-1:0] DataOut; reg [DATA_WIDTH-1:0] mem[(1 << ADDR_WIDTH)-1:0]; // always @(Write_ or DataIn or WAddr) if (!Write_) mem[WAddr] = DataIn; wire [DATA_WIDTH-1:0] DataOut = !Read_ ? mem[RAddr] : 'bz; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Single Port SSRAM 1/2 module SPRAM(Clk, Addr, CS_, WE_, OE_, DataIn, DataOut); // parameter DATA_WIDTH = 16, ADDR_WIDTH = 16; // input [DATA_WIDTH-1:0] DataIn; input [ADDR_WIDTH-1:0] Addr; input Clk, CS_, WE_, OE_; // output [DATA_WIDTH-1:0] DataOut; // reg [DATA_WIDTH-1:0] DataInint, DataOut; reg [ADDR_WIDTH-1:0] AddrInt; reg [DATA_WIDTH-1:0] Mem[(1 << ADDR_WIDTH)-1:0]; reg CSint_, WEint_, OEint_; // ΗΥ-220 - Καλοκαιρινός Γιώργος

Single Port SSRAM 2/2 // always @(posedge Clk) begin AddrInt <= Addr; CSint_ <= CS_; WEint_ <= WE_; OEint_ <= OE_; DataInint <= DataIn; end always @(posedge Clk) if(~CSint_ & ~WEint_) Mem[AddrInt] = DataInint; // always @(OEint_ or CSint_ or AddrInt) DataOut = #`dh (~OEint_&~CSint_) ? Mem[AddrInt] : 'bz; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος

Dual Port SSRAM 1/3 module DPRAM(Clk1, Addr1, CS1_, WE1_, OE1_, DataIn1, DataOut1, Clk2, Addr2, CS2_, WE2_, OE2_, DataIn2, DataOut2); // parameter DATA_WIDTH = 16, ADDR_WIDTH = 16; input [DATA_WIDTH-1:0] DataIn1, DataIn2; input [ADDR_WIDTH-1:0] Addr1, Addr2; input Clk1, Clk2, CS1_, CS2_, WE1_, WE2_, OE1_, OE2_; output [DATA_WIDTH-1:0] DataOut1, DataOut2; // reg [DATA_WIDTH-1:0] DataIn1int, DataOut1, DataIn2int, DataOut2; reg [ADDR_WIDTH-1:0] Addr1int, Addr2int; reg [DATA_WIDTH-1:0] Mem[(1 << ADDR_WIDTH)-1:0]; reg CS1int_, WE1int_, OE1int_, CS2int_, WE2int_, OE2int_; // ΗΥ-220 - Καλοκαιρινός Γιώργος

Dual Port SSRAM 2/3 // always @(posedge Clk1) begin Addr1int <= Addr1; CS1int_ <= CS1_; WE1int_ <= WE1_; OE1int_ <= OE1_; DataIn1int <= DataIn1; end always @(posedge Clk1) if(~CS1int_&~WE1int_) Mem[Addr1int] = DataIn1int; // always @(OE1int_ or CS1int_ or Addr1int or Clk1) DataOut1 = #1 (~OE1int_&~CS1int_) ? Mem[Addr1int] : 'bz; // ΗΥ-220 - Καλοκαιρινός Γιώργος

Dual Port SSRAM 3/3 // always @(posedge Clk2) begin Addr2int <= Addr2; CS2int_ <= CS2_; WE2int_ <= WE2_; OE2int_ <= OE2_; DataIn2int <= DataIn2; end always @(posedge Clk2) if(~CS2int_&~WE2int_) Mem[Addr2int] = DataIn2; // always @(OE2int_ or CS2int_ or Addr2int or Clk2) DataOut2 = #1 (~OE2int_&~CS2int_) ? Mem[Addr2int] : bz; // endmodule ΗΥ-220 - Καλοκαιρινός Γιώργος