Single Event Upsets in Digital VLSI Circuits

200 likes | 347 Views

Single Event Upsets in Digital VLSI Circuits. EYES Summer Internship Program 2007 University of New Mexico Vinay Jain Dr. Payman Zarkesh-Ha Final Year Undergraduate Assistant Professor ECE

Single Event Upsets in Digital VLSI Circuits

E N D

Presentation Transcript

Single Event Upsets in Digital VLSI Circuits EYES Summer Internship Program 2007 University of New Mexico Vinay Jain Dr. Payman Zarkesh-Ha Final Year Undergraduate Assistant Professor ECE Indian Institute of Technology Kanpur University of New Mexico

Outline • Introduction • Soft-Spot Analysis • Inverter Model proposed • Simulation Results • Extension of the Model

Introduction • Origin • Soft errors, Single Event Transients (SET) and Single Event Upsets (SEU) • Techniques to reduce SET propagation • Softness of a node Origin of Soft errors: cosmic neutrons and α- particles Particle Strike in CMOS Digital VLSI circuits. SET and SEU

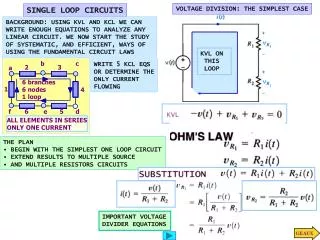

Soft-Spot Analysis • Timing Masking Factor, TN • Tendency of a node to allow noise in particular time window • Computed using time delays and sensitive window durations of various gates in the path • Logic Masking Factor, LN • Likelihood for noise at a node to logically reach the storage element • Computed using probability of nodes in the path to acquire certain states • Electrical Masking Factor, EN • Ability of a node to allow noise propagation with enough strength • Computed from the characteristics of Noise Rejection Curves • Overall Softness, SN • SN = TN*LN*EN

Noise Rejection Curves Noise Rejection Curves for an inverter and its effects as Load and Size of the inverter is varied

Inverter Model Proposed Model proposed is- replacement of MOS transistors with constant current sources the DC value of which is the average drain currents of the transistors

A. Velocity Saturation Effects in short channel MOSFETs υ = μ.E / (1 + E / EC) , E < EC = υSAT , E > EC where EC = 2 υSAT/ μ VDSATn = VGTn / (1 + VGTn / ECn.Ln) for short channel (small Ln) saturates to VDSATn = ECn.Ln as VGTn is increased = VGTn, long channel (large Ln)

IDSATn = υSATn.Cox.Wn.( VGTn -VDSATn ) = υSATn.Cox.Wn.(VGTn)2 / (VGTn + ECn.Ln) ~ υSATn. Cox.Wn.(VGTn) for small channel MOSFETs (small Ln) ~ υSATn. Cox.Wn.(VGTn)2 / ECn.Ln for long channel MOSFETs (large Ln)

B. Voltage Transfer Characteristic Noise can propagate only when input pulse has magnitude greater than Vm Voltage Transfer Characteristic for an Inverter (INVx1)

C. Average Current Model ID VDS characteristic for an inverter (INVx1) for gate Voltage greater than Vm IN =(IDn)avg = IDSATn(1 + λn(VDD + Vm)/ 2) IN = Cn*. IDSATn where Cn* = 1 + λn(VDD + Vm)/ 2

<VDSATp> = VDSATp at VG = (VDD + Vm)/ 2 IP1= IDSATp. (1+λp.<VDSATp>) IP2= IDSATp. (1+λp.(VDD - Vm)) IP= (IDp)avg = [ (IP1/2).<VDSATp> + {(IP1+IP2)/2}.(VDD – Vm – <VDSATp>) ] / (VDD – Vm ) = IDSATp.(1 + λp(VDD - Vm)/ 2 – <VDSATp>/(2.(VDD - Vm)) ) Thus, IP = Cp*. IDSATp where Cp* = 1 + λp(VDD - Vm)/ 2 – <VDSATp>/(2.(VDD - Vm))

Thus, we have IN = Cn*IDSATn& IP = Cp*IDSATp where both Cn* & Cp* are constants and close to unity. We can now calculate TC as the minimum duration required for a noise pulse of height VC volts, to propagate through the inverter as TC = CL.(VDD - Vm)/(IN - IP) with VG = VC The above equation gives a relation between TC and VC as a function of only Gate size (W and L) of p-MOS and n-MOS.

Simulation Results Noise Rejection Curves comparison for INVx1 (Load = 200fF) Time taken for simulation by matlab = 0.074 sec Time taken for simulation by Tspice = 4.48 sec Mean %error = 11.59% Noise Rejection Curves comparison for INVx2 (Load = 200fF) Time taken for simulation by matlab = 0.077 sec Time taken for simulation by Tspice = 4.45 sec Mean %error = 4.68%

Noise Rejection Curves comparison for INVx8 (Load = 200fF) Time taken for simulation by matlab = 0.069 sec Time taken for simulation by Tspice = 4.42 sec Mean %error = 17.65% Noise Rejection Curves comparison for INVx4 (Load = 200fF) Time taken for simulation by matlab = 0.074 sec Time taken for simulation by Tspice = 4.61 sec Mean %error = 6.70%

Extension of the model Modeling of NAND gates for easy computation of Noise Rejection Curves

Modeling of NOR gates for easy computation of Noise Rejection Curves

Noise Rejection Curves comparison for NANDx1 (Load = 200fF) Time taken for simulation by matlab = 0.078 sec Time taken for simulation by Tspice = 5.05 sec Mean %error = 30.16% Noise Rejection Curves comparison for NORx1 (Load = 200fF) Time taken for simulation by matlab = 0.076 sec Time taken for simulation by Tspice = 5.09 sec Mean %error = 9.23%

References [1] C. Zhao, X. Bai, S. Dey, “A scalable soft spot analysis methodology for compound noise effects in nano-meter circuits,” DAC’04, pp. 894-899, June 2004. [2] C. Zhao, S. Dey, “Improving transient error tolerance of digital VLSI circuits using RObustness COmpiler (ROCO),” International Symposium on Quality Electronic Design, ISQED’06 [3] C.G. Sodini, P. Ko, J. Moll, “The effect of high fields on MOS device and circuit performance,” IEEE transactions on Electron Devices, October 1984, pp.1386-1393 [4] J. M. Rabaey, A. Chandrakasan, B. Nikolic, “Digital Integrated Circuits,” Second edition, 2003