Final project design Simple CPU

Final project design Simple CPU. The basic flow for CPU. Register. 做資料的存取. 32. 32. Instr. Memory. PC. operation. i_addr. i_data. 做資料的存取. Data Memory. The Memory modules. clk. 32. 32. Instr. Memory. Always i_data <= Mem[i_addr]. i_addr. i_data. clk. 32. d_addr.

Final project design Simple CPU

E N D

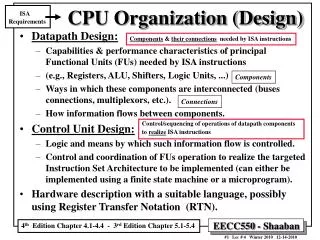

Presentation Transcript

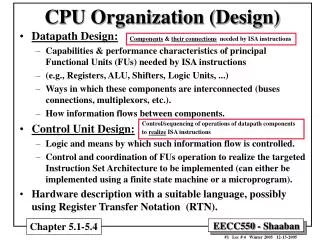

The basic flow for CPU Register 做資料的存取 32 32 Instr.Memory PC operation i_addr i_data 做資料的存取 DataMemory

The Memory modules clk 32 32 Instr.Memory Always i_data <= Mem[i_addr] i_addr i_data clk 32 d_addr When d_rw = 0 : read : d_dataout <= Mem[d_addr] When d_rw = 1 : write : Mem[d_addr]<=d_datain 32 DataMemory d_dataout 32 d_datain d_rw

The hierarchy of our design i_addr i_data d_rw d_addr d_datain d_dataout Instruction Memory Data Memory FINAL Design this block d_addr pc inst dmem_rw d_datain d_dataout 32 32 1 32 32 32

Instruction Set Architecture (3/3) Instr.Memory addr $ra = return address 這裡我們令$R31當$ra來使用 Instr. 0 0 PC Instr. 1 1 Instr. 2 2 PC = PC + 1 Instr. 3 3 :: :: 32 bits

繳交資料 • 繳交日期:6/30 p.m. 12:00 以前 • 繳交資料: • 一份書面報告(word檔) • 簡易說明程式內容及執行結果。 • 組員工作分配。 • 程式檔案 • Verilog 檔 • 檔名請命名成”groupXX.v”, XX是組別號碼。 • Top module 請命名成FINAL。 • 繳交方式: • 與繳交lab作業方式相同,上傳至ftp • 其他: • 若有CPU規格或上傳作業之問題,可寄信或到實驗室找助教

31 • 1 addi $r1,$r0,32---r1=r0+32 • 2 subi $r2,$r1,5----r2=r1-5 • 3 slti $r3,$r0,32---()r3=1 • 4 lw $r4,1($r0)-----r4=DMEM[1+0] • 5 sw $r1,0($r0)-----DMEM[0+0]=r1 • 6 add $r5,$r1,$r2---r5=r1+r2 • 7 slt $r6,$r0,$r1---r6=1 • 8 sll $r7,$r1,1-----r7=r1<<1 • 9 j 13--------------pc=52 • 10 beq $r7,$r7,1-----pc=48 • 11 jr $r31-----------pc=60 • 12 bne $r1,$r0,-2----pc=44 • 13 addi $r8,$r0,8----r8=r0+8 • 14 jal 10-----------pc=40,r31=15*4 • 15 srl $r9,$r1,2-----r9=r1>>2 • 16 sra $r10,$r1,2----r10=r1>>2 • 17 sub $r11,$r1,$r2--r11=r1-r2 • 18 and $r12,$r2,$r4--r12=r2&r4 • 19 or $r13,$r2,$r4---r13=r2 | r4 • 20 xor $r14,$r2,$r4--r14=r2 ^ r4 • 21 andi $r15,$r2,22--r15=r2 & 22 • 22 ori $r16,$r2,22---r16=r2 | 22 32 27 1 6 57 1 64 8 8 8 32 5 3 63 60 60 18

001000_00000_00001_00000_00000_100000 • //addi $r1,$r0,32---r1=32 • 001001_00001_00010_00000_00000_000101 • //subi $r2,$r1,5----r2=27 • 001010_00000_00011_00000_00000_100001 • //slti $r3,$r0,32---r3=1 • 100011_00000_00100_00000_00000_000001 • //lw $r4,1($r0)-----r4=DMEM[1] • 101011_00000_00001_00000_00000_000000 • //sw $r1,0($r0)-----DMEM[0]=r1 • 000000_00001_00010_00101_00000_100000 • //add $r5,$r1,$r2---r5=r1+r2

000000_00000_00001_00110_00000_101010 • //slt $r6,$r0,$r1---r6=1 • 000000_00001_00000_00111_00001_000000 • //sll $r7,$r1,1-----r7=64 • 000010_00000_00000_00000_00000_001101 • //j13--------------pc=52 • 000100_01001_01001_00000_00000_000001 • //beq $r7,$r7,1-----pc=48 • 000000_00000_00000_00000_00000_001000 • //jr $r31-----------pc=60 • 000101_00000_00001_11111_11111_111110 • //bne $r1,$r0,-2----pc=44

001000_00000_01000_00000_00000_001000 • //addi $r8,$r0,8----r8=8 • 000011_00000_00000_00000_00000_001010 • //jal 10------------pc=40,r31=60 • 000000_00001_00000_01001_00010_000010 • //srl $r9,$r1,2-----r9=8 • 000000_00001_00000_01010_00010_000011 • //sra $r10,$r1,2----r10=8 • 000000_00001_00010_01011_00010_100010 • //sub $r11,$r1,$r2--r11=5 • 000000_00010_00100_01100_00000_100100 • //and $r12,$r2,$r4--r12=3

000000_00010_00100_01101_00000_100101 • //or $r13,$r2,$r4---r13=63 • 000000_00010_00100_01110_00000_100110 • //xor $r14,$r2,$r4--r14=60 • 001100_00010_01111_00000_00000_010110 • //andi $r15,$r2,22--r15=18 • 001101_00010_10000_00000_00000_010110 • //ori $r16,$r2,22---r16=31