MOSFET 新材料

MOSFET 新材料. ( a ) 高介电常数(高 k )栅介质薄膜的制备技术及其工艺研究 :

MOSFET 新材料

E N D

Presentation Transcript

MOSFET新材料 • (a)高介电常数(高k)栅介质薄膜的制备技术及其工艺研究: • 在相同等效氧化层厚度的情况下,高k栅介质具有更厚的物理厚度,有助于减小栅与沟道间的直接隧穿电流,降低器件功耗,提高器件可靠性。2007年,高k栅介质/金属栅技术被Intel公司在其45nm工艺制程中率先采用。采用高k栅介质/金属栅结构,可有效克服传统多晶硅/SiON结构面临的难以逾越的困难,是集成电路沿摩尔定律发展的有力保证。近几年,高k栅介质材料领域的研究成果层出不穷,性能优良的新型高k栅介质材料不断涌现。现今,高k栅介质材料的研究热点主要集中于Hf基高k栅介质材料的研究,其中以掺杂型Hf基高k栅介质材料为主,包括HfON、HfAlO、HfAlON、HfSiO、HfSiON、HfTaO和HfTaON等。

(b)金属栅的制备技术及其工艺研究。 • 难熔金属栅能够很好的解决多晶硅栅电极存在的问题,因而被认为是最有希望的取代多晶硅栅电极的下一代栅电极材料。为了满足半导体工艺的要求,金属栅材料应满足以下几点要求:(1)良好的导电性;(2)高热稳定性。在高温下要与介质材料保持良好的热力学稳定性,不与下层的二氧化硅或高k栅介质发生发应;具有很高的熔点,能够经受源漏杂质激活退火等热过程;(3)与栅介质层之间要有好的黏附性,与其周围材料间的应力要小;(4)与CMOS工艺兼容性好;(5)具有合适的功函数和栅功函数调节能力。

(c)应变硅和高迁移率沟道材料的制备技术及其工艺。(c)应变硅和高迁移率沟道材料的制备技术及其工艺。 • 应变硅技术通过在整个衬底或者局部区域产生应力,来提高载流子的迁移率。应变沟道目前主要存在两类途径:一类称为全局应力,通过衬底和沟道之间的晶格失配从而在沟道区形成应力,主要有应变Si、应变SiGe、应变SiC沟道;另一类方法称为局部应力,通过对工艺作局部的改动从而在沟道中引进应力,这种方法操作简单,目前在工业界获得了广泛的应用,主要有覆盖薄膜应力,栅极存储应力, SiGe、SiC源漏合金应力等。新的高迁移率沟道材料也是最近一段时间的研究热点。

(d)新结构器件的研究。 • 人们已经提出许多不同于传统平面结构的新结构器件。如:迁移率增强器件、超薄体SOI器件、垂直晶体管、源漏工程器件、FinFET等,其中目前最成功要算是双栅FinFET。双栅FinFET最早是由加州大学Berkeley分校C.Hu领导的器件组开发的新结构双栅器件,它是做在SOI的衬底上,问世之后便受到世界各国研究者的广泛关注;在近几年的IEEE IEDM和VLSI symp等集成电路领域的重要会议上,FinFET 都成为关注的焦点。FinFET结构本质上属于一种准平面结构,制备工艺相对比较简单,但是其栅宽在垂直于平面的方向,不容易做大。源漏的电阻会比较大。这种结构相较于其它新型结构器件比较容易制备,与CMOS兼容性很好。因此被认为是一种很有前途的器件结构形式。

不同MOSFET模型应用场合 Level 1 简单MOSFET模型 Level 2 2m 器件模拟分析 Level 3 0.9m 器件数字分析 BSIM 1 0.8m 器件数字分析 BSIM 2 0.3m 器件模拟与数字分析 BSIM 3 0.5m 器件模拟分析与0.1m 器件数字分析 Level=6 亚微米离子注入器件 Level=50 小尺寸器件模拟电路分析 Level=11 SOI器件 对电路设计工程师来说, 采用什么模型参数在很大程度上还取决于能从相应的工艺制造单位得到何种模型参数.

MOSFET一级模型直流特性涉及的模型参数 VTO VTO衬底零偏置时源阈值电压 KP 本征跨导参数 GAMMA 体效应阈值系数 PHI 2F强反型使的表面势垒高度 LAMBDA 沟道长度调制系数 UO µo/µn表面迁移率 L 沟道长度 LD 沟道长度方向上横向扩散长度 W 沟道宽度 TOX TOX栅氧化层厚度 TPG 栅材料类型 NSUB NSUB衬底(阱)掺杂浓度 NSS NSS表面态密度.

台积电公司某一批0.35m CMOS工艺NMOS器件的Star-HSpice参数(命名为CMOSN的NMOS模型库Spice文件) .MODEL CMOSN NMOS (LEVEL = 49 +VERSION = 3.1 TNOM= 27 TOX = 7.6E-9 +XJ = 1E-7 NCH = 2.3579E17 VTH0 = 0.5085347 +K1 = 0.5435268 K2 = 0.0166934 K3 = 2.745303E-3 +K3B = 0.6056312 W0 = 1E-7 NLX = 2.869371E-7 +DVT0W = 0 DVT1W = 0 DVT2W = 0 +DVT0 = 1.7544494 DVT1 = 0.4703288 DVT2 = -0.0394498 +U0 = 489.0696189 UA = 5.339423E-10 UB = 1.548022E-18 +UC = 5.795283E-11 VSAT = 1.191395E5 A0 = 0.8842702 +AGS = 0.1613116 B0 = 1.77474E-6 B1 = 5E-6 +KETA = 5.806511E-3 A1 = 0 A2 = 1

台积电公司某一批0.35m CMOS工艺NMOS器件的Star-HSpice参数(命名为CMOSN的NMOS模型库Spice文件)(续) +RDSW = 1.88264E3 PRWG = -0.105799 PRWB = -0.0152046 +WR = 1 WINT = 7.381398E-8 LINT = 1.030561E-8 +XL = -2E-8 XW = 0 DWG = -1.493222E-8 +DWB = 9.792339E-9 VOFF = -0.0951708 NFACTOR = 1.2401249 +CIT = 0 CDSC = 4.922742E-3 CDSCD = 0 +CDSCB = 0 ETA0 = 2.005052E-3 ETAB = 5.106831E-3 +DSUB = 0.2068625 PCLM = 1.9418893 PDIBLC1 = 0.2403315 +PDIBLC2 = 5.597608E-3 PDIBLCB = -4.18062E-4 DROUT = 0.5527689 +PSCBE1 = 4.863898E8 PSCBE2 = 1.70429E-5 PVAG = 1.0433116 +DELTA = 0.01 MOBMOD = 1 PRT = 0 +UTE = -1.5 KT1 = -0.11 KT1L = 0 +KT2 = 0.022 UA1 = 4.31E-9 UB1 = -7.61E-18

台积电公司某一批0.35m CMOS工艺NMOS器件的Star-HSpice参数(命名为CMOSN的NMOS模型库Spice文件)(续) +UC1 = -5.6E-11 AT = 3.3E4 WL = 0 +WLN = 1 WW = -1.22182E-15 WWN = 1.137 +WWL = 0 LL = 0 LLN = 1 +LW = 0 LWN = 1 LWL = 0 +CAPMOD = 2 XPART = 0.4 CGDO = 1.96E-10 +CGSO = 1.96E-10 CGBO = 0 CJ = 9.384895E-4 +PB = 0.7644361 MJ = 0.3394296 CJSW = 2.885151E-10 +PBSW = 0.8683237 MJSW = 0.1808065 PVTH0 = -0.0101318 +PRDSW = -159.9288563 PK2 = -9.424037E-4 WKETA = 4.696914E-3 +LKETA = -6.965933E-3 PAGS = 0.0718 NQSMOD = 1 +ELM = 5 ) *END CMOSN

Short channel effect • 二维电势分布 VGS(th)漂移 亚阈电流上升 • 高电场 Vsat 寄生双极晶体管效应 热载流子

Theory • Constant Electric Field理论(CE) • Constant Voltage理论(CV) • Quasi-Constant Voltage理论(QCV)

CE理论 • 器件尺寸、电源电压及衬底浓度均按一个比例因子而变化,即所有水平方向和垂直方向的器件尺寸均按1/缩小( 1)。与此同时,为了保持器件中各处电场强度不变,所有工作电压均按同样比例降低倍。为了按同样比例缩小器件内各个耗尽层宽度,衬底浓度应提高倍。

Figure:Cross-sectional view of a self-aligned poly-silicon gate transistor with LOCOS isolation

LDD As the channel length becomes smaller, the junction electric fields become larger. One approach that reduces these breakdown effects is to alter the doping profile of the drain contact. Peak electric field changes.

双极与CMOS的兼容有三方面的含义: 1。器件级的兼容 2。功能级的兼容 3。新的Bi-CMOS单元电路

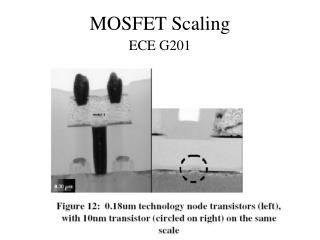

Nano MOS 基本问题: 1。器件尺寸缩小对工艺技术的挑战 2。栅氧化层减薄的限制 3。量子效应的影响 1 2 3 4 4。杂质随机分布的影响 5。阈值电压减小的限制 6。源、漏区串联电阻的影响

As indicated by the ITRS roadmap scaling of conventional bulk CMOS transistors is becoming more and more difficult for the 45 nm technology node and beyond. This is because very high doping concentrations in the channel and ultra shallow junctions are needed in the channel in order to suppress short channel effects. Another critical issue is that probably high k dielectrics will be needed with an equivalent oxide thickness below 1nm necessary to achieve the desired on currents in the range of 1mA/µm at power supply voltages below 1V. Although several transistors with extremely short channels have been demonstrated in the literature, they all suffer from lack of performance. Therefore, novel transistor concepts for CMOS are under investigation.