Background

100 likes | 236 Views

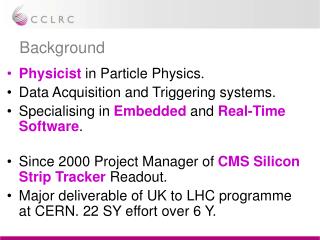

Background. Physicist in Particle Physics. Data Acquisition and Triggering systems. Specialising in Embedded and Real-Time Software . Since 2000 Project Manager of CMS Silicon Strip Tracker Readout. Major deliverable of UK to LHC programme at CERN. 22 SY effort over 6 Y.

Background

E N D

Presentation Transcript

Background • Physicist in Particle Physics. • Data Acquisition and Triggering systems. • Specialising in Embedded and Real-Time Software. • Since 2000 Project Manager of CMS Silicon StripTracker Readout. • Major deliverable of UK to LHC programme at CERN. 22 SY effort over 6 Y.

TBU Electronics – CMS FED • Major electronics system for CMS experiment Silicon Strip Tracker Off-Detector readout at the Large Hadron Collider facility CERN Geneva • 500Large Complex Electronic Boards (FEDs) • ~ 45 K ADC channels • Massively Parallel FPGA based Processing > 1 TERA-BYTE / sec(~2,000 CDROMs/sec) • Designed, implemented and tested by Technology ~ £ 4 Million project over several years in collaboration with Imperial College, PPD, CERN. • Manufactured in Partnership with UK IndustryeXception EMS Ltd received CMS Gold Award 2006 • Knowledge Transfer • Delivered to CERN on budget & ahead of schedule x 500 RAL CMS Awards Commissioning at CERN Slide shown at CEO Staff Talk July 2006

CMS FED - Project Manager Role • Led project from Feasibility stage through Design, Implementation to Delivery. Leading team of ~ 6 engineers • Low-level software for FPGA design verification. • Major role in all activities from capturing Requirements to Board & FPGA design specification, manufacture and Qualification. • Reporting to CMS UK Management Committee,CMS/Trackermanagement CERN. • Presentations at International Conferences. • Maintained effective collaboration with project stakeholders, Imperial College, PPD, CERN. • Negotiated and managed FED manufacturing contract £1.75M on behalf of CMS UK and CERN.

TBU – Electronics Systems Design Group • Section leader in ESDG (2 staff). • Deputy Group Leader (15 staff). • Control Group Budget. • Manage SLHC, ASIC (non MAPS) accounts. • In charge of Communications, Software Training, PC and FPGA related purchasing. • Active formulating group Strategy via Business Plan.

Future Roles • Complete Installation and Commissioning of FEDs for LHC pilot run 2007. • Lead R&D team in Embedded Systems based on FPGAs. • Apply to New Challenges and Opportunities: • SLHC, ILC • Diamond, XFEL +… • Offer to CCLRC : Technical expertise, Management abilities and Scientific world view.

Tracker Readout On Detector (Radiation Hard) Readout Silicon Tracking detector. ~ 10 million Silicon Strip channels ON Detector: APV25 pipeline chips @ L1 Trigger: MUX APV Frame output Analogue Data readout via Optical links (100 kHz APV Frames: Header + Strip Data) OFF Detector: Front-End Drivers (FED) Digitise / Zero Suppress / DAQ readout ~ 500 x 9U VME64x boards (incl spares) 96 ADC channel boards Each 25 K channels per event. ~ 3 GB/s input ~ 50 MB/s/% output 25 Front-End Hybrid Hybrid Silicon Strips 70m FPGA DAQ Counting Room VME 9U FEDs

Large Complex Electronics Board VME And Tracker needs 500 of them Major manufacturing task Optical Hit Finding Event Builder Analogue Output: CDAQ Digital 34 x FPGAs <= 200 Mbytes/sec Data Reduction & Processing Input: Tracker FEnds 25K MUX strips to ~100 ADC channels @ 3 Gbytes/sec Digital Logic Re-Programmable Field Programmable Gate Arrays Firmware (VHDL, Verilog) Software NB System Interfaces critical Tracker FE, DAQ, Trigger ... System Architecture NB One FED board is doing the job of many crates of electronics of tracker readout on last generation of HEP experiments eg HERA Q. How to support a Board with re-programmable digital logic during operation for 10 years ? ...

FED Quality Assurance 0. Quality Controls during Assembly process AOI, X-ray 1. Custom CMS Tests At Assembly Plant Boundary Scan Analogue AssemblyCompany FED 2. Tests at RAL eXception EMS Ltd UK Optical, SLINK, Full crate 3. Tests at CERN Prevessin 904 B186 Tracker Integration VME SLINK Transition card RAL Test Rig 4. Installation at CMS USC55 CERN Test Rig “Pipeline” with each stage taking ~ 1 month and containing ~ 50 FEDs

FPGAs CPUs Field Programmable Gate Array Xilinx Virtex 4 System on Chip Hardware Programming Language RTL; VHDL + Embedded IP Blocks e.g. PPC, Ethernet MAC Software Programming Language; C System Partitioning ; Operating Systems SLHC DAQ?