Chapter Five The Processor: Datapath and Control

Chapter Five The Processor: Datapath and Control. The Processor: Datapath & Control. We're ready to look at an implementation of the MIPS Simplified to contain only: memory-reference instructions: lw, sw arithmetic-logical instructions: add, sub, and, or, slt

Chapter Five The Processor: Datapath and Control

E N D

Presentation Transcript

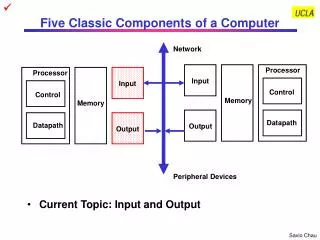

The Processor: Datapath & Control • We're ready to look at an implementation of the MIPS • Simplified to contain only: • memory-reference instructions: lw, sw • arithmetic-logical instructions: add, sub, and, or, slt • control flow instructions: beq, j • Não implementadas: mult, div, jal, fp • Generic Implementation: • use the program counter (PC) to supply instruction address • get the instruction from memory • read registers • use the instruction to decide exactly what to do • All instructions use the ALU after reading the registers: • memory-reference (sw lw), arithmetic, control flow

falling edge cycle time rising edge State Elements • Unclocked vs. Clocked • Clocks used in synchronous logic • when should an element that contains state be updated?

S t a t e S t a t e e l e m e n t C o m b i n a t i o n a l l o g i c e l e m e n t 1 2 C l o c k c y c l e Our Implementation • An edge triggered methodology • Typical execution: • read contents of some state elements, • send values through some combinational logic • write results to one or more state elements

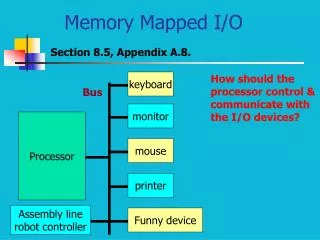

RD WR Dados Endereço Register File (e Memória) Register File:built out D-FF • Memória: • acesso Mem[addr]

IR Mem[PC] PC PC + 4 Fetch ou busca lw, sw arit slt beq N N R1 Mem[R2+off] R1 R2 op R3 R2<R3? R1=R2? S S R1 0 R1 1 PC PC +off Uma visão simplificada Dados: lw, swArit: add, sub, .. op Log: slt Desvio: beq lw $t1, 100($t2) add $t1, $t2, $t3 slt $t1, $t2, $t3 beq $t1, $t2, label

More Implementation Details • Primeira abordagem: 1 período de clock por instrução • Abstract / Simplified View:Two types of functional units: • elements that operate on data values (combinational) • elements that contain state (sequential) exec de uma instrução

I n s t r u c t i o n a d d r e s s P C I n s t r u c t i o n A d d S u m I n s t r u c t i o n m e m o r y M e m W r i t e a . I n s t r u c t i o n m e m o r y b . P r o g r a m c o u n t e r c . A d d e r R e a d A d d r e s s d a t a 1 6 3 2 S i g n e x t e n d D a t a W r i t e m e m o r y d a t a M e m R e a d A L U c o n t r o l 5 3 R e a d r e g i s t e r 1 R e a d a . D a t a m e m o r y u n i t b . S i g n - e x t e n s i o n u n i t d a t a 1 5 R e g i s t e r R e a d Z e r o r e g i s t e r 2 n u m b e r s R e g i s t e r s D a t a A L U A L U 5 W r i t e r e s u l t r e g i s t e r R e a d d a t a 2 W r i t e D a t a d a t a R e g W r i t e a . R e g i s t e r s b . A L U Simple Implementation • Include the functional units we need for each instruction Why do we need this stuff?

A d d 4 R e a d P C a d d r e s s I n s t r u c t i o n I n s t r u c t i o n m e m o r y Fetch

A L U o p e r a t i o n 3 R e a d r e g i s t e r 1 R e a d d a t a 1 R e a d Z e r o r e g i s t e r 2 I n s t r u c t i o n R e g i s t e r s A L U A L U W r i t e r e s u l t r e g i s t e r R e a d d a t a 2 W r i t e d a t a R e g W r i t e Tipo R

A L U o p e r a t i o n 3 R e a d r e g i s t e r 1 M e m W r i t e R e a d d a t a 1 R e a d Z e r o r e g i s t e r 2 I n s t r u c t i o n A L U R e g i s t e r s A L U R e a d W r i t e r e s u l t A d d r e s s d a t a r e g i s t e r R e a d d a t a 2 W r i t e D a t a d a t a m e m o r y W r i t e R e g W r i t e d a t a 1 6 3 2 S i g n M e m R e a d e x t e n d Referência a Memória

P C + 4 f r o m i n s t r u c t i o n d a t a p a t h A d d S u m B r a n c h t a r g e t S h i f t l e f t 2 A L U o p e r a t i o n 3 R e a d r e g i s t e r 1 I n s t r u c t i o n R e a d d a t a 1 R e a d r e g i s t e r 2 T o b r a n c h R e g i s t e r s A L U Z e r o c o n t r o l l o g i c W r i t e r e g i s t e r R e a d d a t a 2 W r i t e d a t a R e g W r i t e 1 6 3 2 S i g n e x t e n d beq

P C S r c M A d d u x A L U A d d 4 r e s u l t S h i f t l e f t 2 R e g i s t e r s A L U o p e r a t i o n 3 R e a d M e m W r i t e A L U S r c R e a d r e g i s t e r 1 P C R e a d a d d r e s s R e a d M e m t o R e g d a t a 1 Z e r o r e g i s t e r 2 I n s t r u c t i o n A L U A L U R e a d W r i t e R e a d A d d r e s s r e s u l t M d a t a r e g i s t e r d a t a 2 M u I n s t r u c t i o n u x W r i t e m e m o r y D a t a x d a t a m e m o r y W r i t e R e g W r i t e d a t a 3 2 1 6 S i g n M e m R e a d e x t e n d Building the Datapath • Use multiplexors to stitch them together

ALUs e Multiplexadores • ALU genérica: R1 R2 op R3 • ALU soma para endereço instrução: PC + 4 • ALU soma para endereço de desvio: PC + SignExt (ShiftLeft (Offset)) • MUX 2:1 para escolher segundo operando da ALU genérica • R2 • SignExt (Offset) • MUX 2:1 para escolher o que será carregado no PC • PC + 4 • PC + SignExt (ShiftLeft (Offset)) • MUX 2:1 para escolher qual é a origem do dado a ser escrito no Banco de Registradores • lido da memória • resultado da operação da ALU genérica

Control • Selecting the operations to perform (ALU, read/write, etc.) • Controlling the flow of data (multiplexor inputs) • Information comes from the 32 bits of the instruction • Example: add $8, $17, $18 Instruction Format: 000000 10001 10010 01000 00000 100000 op rs rt rd shamt funct • ALU's operation based on instruction type and function code

Control • e.g., what should the ALU do with this instruction • Example: lw $1, 100($2) 35 2 1 100 op rs rt 16 bit offset • ALU control input000 AND 001 OR 010 add 110 subtract 111 set-on-less-than • Why is the code for subtract 110 and not 011?

2 6 ALUop ALU Control OPCODE Unid. Contr.(parte) 3 funct 6 ALU IR OPCODE Funct. Controle da ALU Binv - cod

Campos da instrução e MUX adicional • 2 registradores a serem lidos em todos os tipos: • campos rs (25-21) e rt (20-16) • offset para beq, lw e sw: • (15-0) • Registradores de destino (write register) em dois lugares: • lw e sw: rt (20-16) • Tipo R: rd (15-11) • Necessário MUX controlado por RegisterDestination: RegDst

Unidade de Controle Formato R: 000 000 lw: 100 011 sw: 101 011 beq: 000 100

S t a t e S t a t e e l e m e n t C o m b i n a t i o n a l l o g i c e l e m e n t 1 2 C l o c k c y c l e Our Simple Control Structure • All of the logic is combinational • We wait for everything to settle down, and the right thing to be done • ALU might not produce “right answer” right away • we use write signals along with clock to determine when to write • Cycle time determined by length of the longest path We are ignoring some details like setup and hold times

P C S r c 1 M A d d u x A L U 0 4 A d d r e s u l t S h i f t R e g W r i t e l e f t 2 I n s t r u c t i o n [ 2 5 – 2 1 ] R e a d r e g i s t e r 1 R e a d M e m W r i t e R e a d P C d a t a 1 I n s t r u c t i o n [ 2 0 – 1 6 ] a d d r e s s R e a d M e m t o R e g A L U S r c r e g i s t e r 2 Z e r o I n s t r u c t i o n R e a d 1 A L U A L U [ 3 1 – 0 ] 1 R e a d W r i t e d a t a 2 1 A d d r e s s r e s u l t M r e g i s t e r M d a t a u M I n s t r u c t i o n u I n s t r u c t i o n [ 1 5 – 1 1 ] x W r i t e u x m e m o r y R e g i s t e r s x 0 d a t a 0 D a t a 0 W r i t e m e m o r y R e g D s t d a t a 1 6 3 2 S i g n I n s t r u c t i o n [ 1 5 – 0 ] e x t e n d A L U M e m R e a d c o n t r o l I n s t r u c t i o n [ 5 – 0 ] A L U O p Single Cycle Implementation • Calculate cycle time assuming negligible delays except: • memory (2ns), ALU and adders (2ns), register file access (1ns)

J u m p a d d r e s s [ 3 1 – 0 ] I n s t r u c t i o n [ 2 5 – 0 ] S h i f t l e f t 2 2 6 2 8 0 1 M M P C + 4 [ 3 1 – 2 8 ] u u x x A L U A d d 1 0 r e s u l t A d d S h i f t R e g D s t l e f t 2 J u m p 4 B r a n c h M e m R e a d I n s t r u c t i o n [ 3 1 – 2 6 ] M e m t o R e g C o n t r o l A L U O p M e m W r i t e A L U S r c R e g W r i t e I n s t r u c t i o n [ 2 5 – 2 1 ] R e a d R e a d r e g i s t e r 1 P C R e a d a d d r e s s d a t a 1 I n s t r u c t i o n [ 2 0 – 1 6 ] R e a d Z e r o r e g i s t e r 2 I n s t r u c t i o n 0 R e g i s t e r s A L U R e a d A L U [ 3 1 – 0 ] 0 R e a d W r i t e M d a t a 2 A d d r e s s r e s u l t 1 d a t a I n s t r u c t i o n r e g i s t e r M u M u m e m o r y x u I n s t r u c t i o n [ 1 5 – 1 1 ] W r i t e x 1 D a t a x d a t a 1 m e m o r y 0 W r i t e d a t a 1 6 3 2 I n s t r u c t i o n [ 1 5 – 0 ] S i g n e x t e n d A L U c o n t r o l I n s t r u c t i o n [ 5 – 0 ] 2 address 31-26 25-0 Adicionando a instrução jump

Problemas com a alternativa de ciclo único • “Vantagem”: CPI = ? • Desempenho? • supor unidades em uso: Memória (2ns), ALU (2ns), Registr (1ns)

Problemas com o ciclo único (2) • Desempenho: • TCK = caminho crítico = 8 ns • velocidade limitada pelo pior caso • Alternativas: • fazer clock com freqüência variável (muito custoso e complicado) • “picar” a instrução em pequenas funções e executá-las em vários ciclos de clock, uma (ou mais) por ciclo • em vez de duração variável de ciclo, número variável • Vantagens do multiciclo: • velocidade: ciclo limitado pela “operação” mais lenta e não pela “instrução” mais lenta • instruções mais simples executam mais rapidamente • economia de hardware • ter apenas 1: ALU, memória, registrador • usar uma vez todos esses, por ciclo