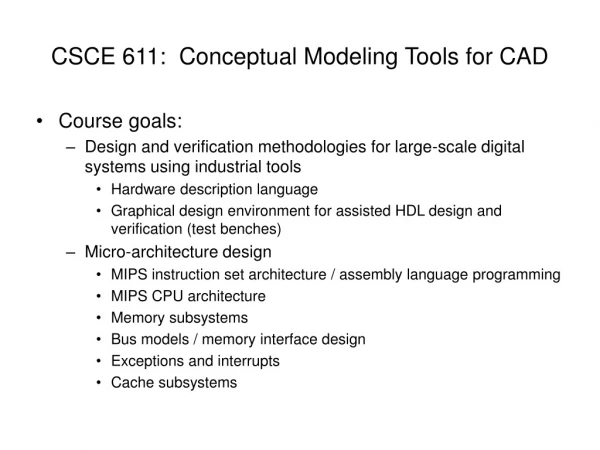

CSCE 611: Conceptual Modeling Tools for CAD

CSCE 611: Conceptual Modeling Tools for CAD. Course goals: Design and verification methodologies for large-scale digital systems using industrial tools Hardware description language Graphical design environment for assisted HDL design and verification (test benches) Micro-architecture design

CSCE 611: Conceptual Modeling Tools for CAD

E N D

Presentation Transcript

CSCE 611: Conceptual Modeling Tools for CAD • Course goals: • Design and verification methodologies for large-scale digital systems using industrial tools • Hardware description language • Graphical design environment for assisted HDL design and verification (test benches) • Micro-architecture design • MIPS instruction set architecture / assembly language programming • MIPS CPU architecture • Memory subsystems • Bus models / memory interface design • Exceptions and interrupts • Cache subsystems

Information • Catalog Description: • 611-Conceptual Modeling Tools for CAD. (3) (Prereq: CSCE 211, 245) Design techniques for logic systems; emphasis on higher-level CAD tools such as hardware description languages and conceptual modeling. • Textbooks and Other Required Material: • Course webpage • Guided tutorials, manuals, lecture slides, ISA/architecture specifications, and additional information • Chapters 4 and 5 from H&P architecture textbook

Outcomes • Design large-scale digital systems using VHDL • Perform behavioral verification using test benches and behavioral simulation • Write and simulate programs in MIPS assembly language using SPIM (an assembler and simulator) • Design a full microprocessor that implements the MIPS instruction set and interfaces a memory system

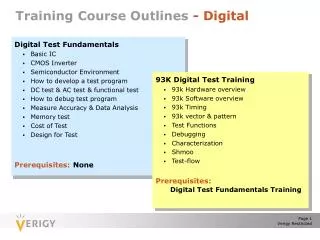

Topics • Topics Covered: • VHDL digital design flow • Design methodologies and techniques • MIPS instruction set architecture • Microarchitecture design • Test bench design • Memory models • Bus models and interface design • Exceptions and interrupts • Memory hierarchy and cache subsystems

Course Structure • Series of 8 lectures spanning approximately ½ of classes • Series of 16 custom online tutorials spanning approximately ¼ of classes • Approximately ¼ of classes spent during project work with guidance from instructor • Lab work: • Lab 1: ALU testbench design • Lab 2: MIPS assembly programming with SPIM assembler/simulator • Lab 3: Multi-cycle CPU design (tested against testbench) • Lab 4: Memory interface and bus design (tested against significant MIPS code) • Lab 5a: Exceptions and interrupts (undergraduate students) • Lab 5b: Primary cache design (graduate students) • Final exam: • 2 hour practicum, requires design of device given specifications • Involves FSM controller interconnected to registers, counters, logic, etc. • Tests knowledge of test of tools • This semester: packet checksum checker

Student Makeup • 11 students • 6 graduate • All CSE students • 2 were formally CIS undergrads (??) • 5 masters, 1 Ph.D. • 5 undergraduate • 1 taking for graduate credit • 2 from EE, 3 from CE • 6 A’s, 2 B’s, 3 C’s

Goals Not Met • The original course outline included an additional signficant project • Pipelined CPU and split primary cache • Could not reach due to extra time needed to present basics of assembly language programming, ISA, archiecture, caches, etc. • Possible to move this to 212? • FPGA implementation