Implementation of a Weighted Round Robin Arbiter on FPGA for Resource Management

This project presents the implementation of a Weighted Round Robin (WRR) arbiter designed for effective resource allocation among multiple clients utilizing an Altera Cyclone® II FPGA. The arbiter prioritizes requests based on configurable weights assigned to each client, enhancing the efficiency of resource management. Implemented on the Altera DE2 board, the system supports real-time adjustable priorities and communicates with the host via UART protocol. The project's scope includes architectural design, VHDL implementation, verification, and testing, ensuring robust performance in resource arbitration.

Implementation of a Weighted Round Robin Arbiter on FPGA for Resource Management

E N D

Presentation Transcript

WRR ARBITERCharacterization Presentation Students: OferSobel Guy Marcus Supervisor: Moshe Porian 16/11/10

Introduction • WRR algorithm arbitrates between clients, requesting usage of the same resource. • Arbitration is performed considering priority weights, assigned to each client. ARBITER

Project Goal Implementing a WRR ARBITER on an FPGA • Implementation will be to Altera Cyclone® II 2C35 FPGA located on an Altera DE2 board • A simulation environment for the WRR arbiter to interact with will also be implemented.

Specifications • Generic number of clients (1 to 4) • Communication with host via UART protocol • Real-Time configurable arbitration weights • Interaction with switches and LEDs • 60 MHZ system clock (generated from board’s 50MHz clock)

Project steps • Determining specifications • Architecture characterization • Conceptual design • VHDL implementation • Verification • Synthesis • Real-Time testing

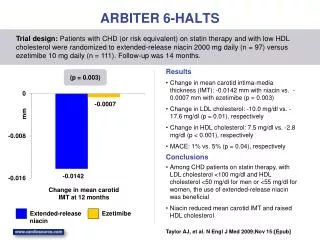

Communication with host – UART Start bit = ‘0’ Data Parity Stop bit = ‘1’ Idle state: Constant marking (‘1’). Start bit: 1 bit of spacing (‘0’). Data: 5 to 8 data bits. Parity: optional parity bit of type ‘odd’ or ‘even’. Stop bit: 1 bit of marking (‘1’). Baud rate: 2400, 4800, 9600, 19200, 38400, 57600 or 115200 bits/sec ±3%

Message Structure A packet of data is constructed in the following way (every block is 1 byte long): scope for CRC Start Address Start 0x00 End 0x15 Type Length Data(1) Data(n) CRC n is determined by ‘Length’ byte write: 0x00 read: 0x1F reply: 0x07 status: 0x18 x8+x7+x6+x4+x2+1

RX path – data flow • Host sends message via RX line. • 2. Receiver packs incoming bits (UART protocol). • 3. Message-Decoder decodes sequences of bytes (message protocol). • Register-Bus-Master executes message according to type: • Writes data to the Register Bus/ Initiates reply message.

TX path – data flow • Register-Bus-Master is signaled to initiate a message. • Register-Bus-Master loads data to the Message-Encoder and encoder FIFO. • Message-Encoder drives the Transmitter with bytes (message protocol). • Transmitter transmits message to the host via the TX line (UART protocol).

Simulation Environment • Simulation using input scripts and output logs • Error/warning tracking • Direct/ Random simulations • Golden model reference • Waves monitoring and recording