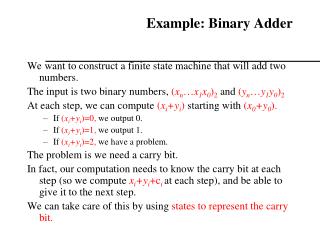

Serial-Adder Example

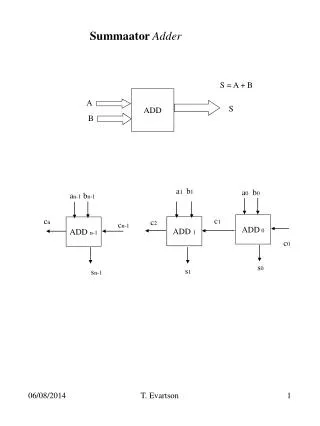

Serial-Adder Example. Review concepts, constructs and features of our 1 st VHDL code Serial-adder code Adder project overview Reading: Bhasker 4.1-4.10 ECE-200 textbook on registers. Tutorial: VHDL Code for a Serial_adder. Entity Architecture std_logic, std_logic_vector data types

Serial-Adder Example

E N D

Presentation Transcript

Serial-Adder Example • Review concepts, constructs and features of our 1st VHDL code • Serial-adder code • Adder project overview • Reading: • Bhasker 4.1-4.10 • ECE-200 textbook on registers

Tutorial: VHDL Code for a Serial_adder • Entity • Architecture • std_logic, std_logic_vector data types • Process statements • process(ck, en) • Process(a, b, state) • Iteration (Loop)

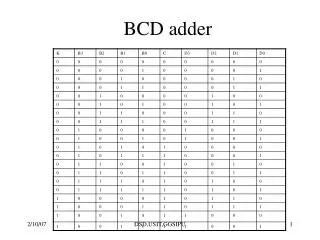

Architecture cout S serial_add A sum U U U U temp U carry state B done En

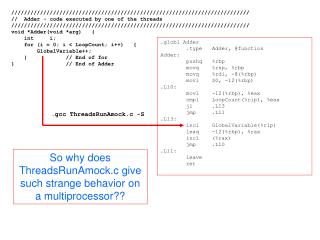

LIBRARY ieee ;USE ieee.std_logic_1164.ALL ; ENTITY serial_adder IS Generic (N : natural := 8); PORT(a,b,clk,en : IN std_logic; s : OUT std_logic_vector(N-1 DOWNTO 0); cout, done : OUT std_logic); END serial_adder; ARCHITECTURE behav OF serial_adder IS SIGNAL state , carry, sum : std_logic; SIGNAL temp : std_logic_vector(N-1 DOWNTO 0); BEGIN

ADD_PROCEDURE: PROCESS (clk, en) VARIABLE counter : INTEGER; BEGIN IF (en = '0') THEN -- resets state <= '0';counter := 0; temp <= (others=>'0'); done <= '0';cout <= '0‘; ELSIF clk = '1' and clk'event THEN IF (counter < N) THEN -- adds state<=carry; --updates carry-in counter:=counter+1; temp(N-1)<=sum; FOR i IN N-2 DOWNTO 0 LOOP temp(i) <= temp(i+1); END LOOP; ELSE -- the addition is done. done <= '1';state <= '0';cout <= carry; END IF; END IF ; END PROCESS ADD_PROCEDURE;

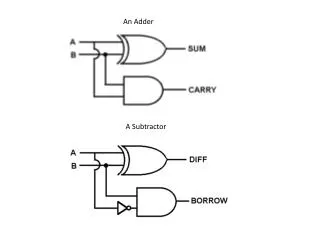

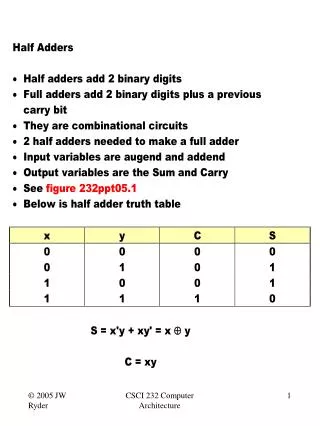

FULL_ADDER: PROCESS(a , b , state) BEGIN sum <= a XOR b XOR state; carry <= (a AND b) OR (a AND state) OR (b AND state); END PROCESS FULL_ADDER; -- Wire the outputs s <= temp; END behav;

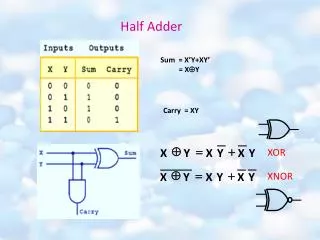

Project Adder Overview • Design Tasks • Serial_adder entity • Shift register • Controller • Adder: wiring the components • Test bench • Block diagram

Adder block diagram simulation cout S RegA serial_add A_bit U U U U sum U U U U temp A RegB U B_bit carry U U U U state done En<=‘1’ B controller Sel<=no_op idle Go=‘0’ n_s reset

cout S serial_add RegA A_bit U U U U U U U U temp A RegB U B_bit U U U U carry done en<=‘0’ B controller Sel<= load load Go=‘1’ n_s reset

cout S serial_adder RegA A_bit 1 0 1 1 0 0 0 0 temp A RegB 0 B_bit 0 1 1 0 carry done B En<=‘1’ controller Sel<=shift shift Go n_s reset

cout S serial_adder RegA A_bit 1 1 0 1 1 0 0 0 temp A RegB 0 B_bit 0 0 1 1 carry done En<=‘1’ B controller Sel<=shift shift Go n_s reset

cout S serial_adder RegA A_bit 1 1 1 0 0 1 0 0 temp A RegB 1 B_bit 0 0 0 1 carry done En<=‘1’ B controller Sel<=shift shift Go n_s reset

cout S serial_adder RegA A_bit 1 1 1 1 0 0 1 0 temp A RegB 1 B_bit 0 0 0 0 carry En<=‘1’ Done=‘1’ B controller Sel<=shift idle Go n_s reset

cout S serial_adder RegA A_bit 1 1 1 1 0 0 0 1 temp A RegB 1 B_bit 0 0 0 0 carry done en B controller sel Go=‘0’ idle n_s reset