Single Event Transient (SET)

Single Event Transient (SET). Single Event Transient (SET). Fraction of a nanosecond to several nanoseconds. From Aerospace. Critical Transient Width vs Feature Size for Unattenuated Propagation. from Mavis. Heavy ion induced negative pulse.

Single Event Transient (SET)

E N D

Presentation Transcript

Single Event Transient (SET) Fraction of a nanosecond to several nanoseconds. From Aerospace

Critical Transient Width vs FeatureSize for Unattenuated Propagation from Mavis

Heavy ion induced negative pulse Double Clocking As a Result of Heavy Ion Induced Pulse Cartoon of clock/logic upset. The device is most sensitive during the transition.

Clock Upset Instrumentation Differential Error Counts Cumulative Error Counts

VCC CSRAM 1 Switch 1 Normally On A ‘High’ Node Contention current path OUT CSRAM 2 B ‘Low’ Node Switch 2 Normally Off Upset to ON GND Driver Contention Due to CSRAM Upset

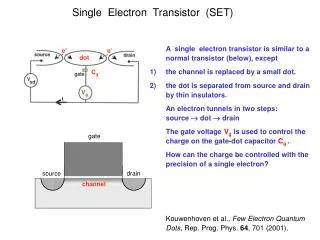

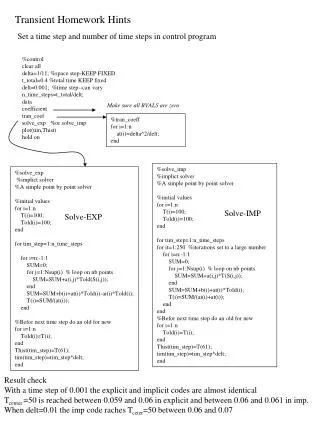

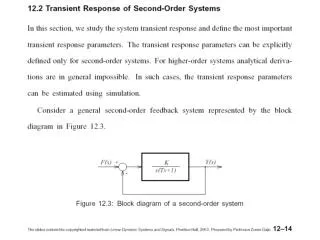

Heavy Ion Hit Transient Pulse Passed One Buffer Data In Mode 1 Transient Upset • Transient pulse higher than half VDC will propagate • Qcrit ~ 0.02pC, or LETth ~ 2MeV-cm2/mg for the worst case

Heavy Ion Hit Hitting Leading Edge CSRAM Hitting Trailing Edge OUT IN Mode 2 Transient Upset (Scenario 1) Q • CSRAM switch is gating the data path. • Metastable (Transient) state in CSRAM due to SEU will modified the signal pulse. • Narrowed signal may disappear and widened signal may cause racing issue. • Hardening increases CSRAM metastable period

Heavy Ion Hit CSRAM QB Q Normally ‘High’ Q A ‘Low’ QB OUT QB B ‘High’ Q Mode 2 Transient Upset (Scenario 2) • CSRAM switch control the MUX. • Metastable (Transient) state in CSRAM due to SEU will temporarily select the wrong input. • Hardening increases CSRAM metastable period.

SET Summary: OMR185, 186 Objective: Provide 2.5V regulation for SX-S FPGAs VIN = 5.0V VOUT = 2.5V (set by resistor) Transient < 3V for CLoad of ~ 20 F Transient > 3V for CLoad of ~ 10 F

Sample LVDO SET WaveformsVIN = 5V; VOUT = 2.5V, RLOAD = 22 OMR185_9924, CLoad: 4.7F OMR185_9924, CLoad: 9.4F