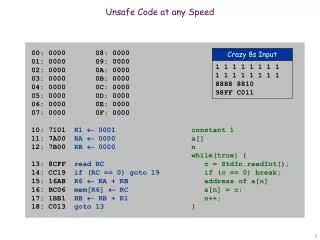

at-speed test

Embedded. Embedded. at-speed test. at-speed test. Issues. Multiple clock domains Multiple frequencies Clock skew between clock domains On-chip PLL generated clocks Multiple PLLs for deskewing Invalidation of delay tests Overtesting (testing of sequential false paths)

at-speed test

E N D

Presentation Transcript

Embedded Embedded at-speed test at-speed test

Issues • Multiple clock domains • Multiple frequencies • Clock skew between clock domains • On-chip PLL generated clocks • Multiple PLLs for deskewing • Invalidation of delay tests • Overtesting (testing of sequential false paths) • Design of scan enable signals • Power dissipation • Ground bounce

Objectives Apply test with system timing in the capture window Clk1 Clk2 Clk3

Multiple frequencies F1 F2 F3 Capture domain F1 F2 F3 F1 Launch domain F2 F3

Multiple clock domains D1 D2 D3 Capture domain D1 D2 D3 D1 Launch domain D2 D3

Single clock domain, single capture last shift capture loading unloading Clk shift mode Sen capture mode • Capture window: from last shift to capture • Scan enable has to propagate to all scan cells in less than one cycle • Overtesting - transitions may be launched from an illegal state • Delay test may be invalidated

Scan enable signal for at-speed scan clock scan enable Scan enable signal designed as a clock tree

Pipelined scan enable signal clock scan enable

Speed of loading S C S S Clock suppression Clock suppression • Only the timing in capture window is crucial to at-speed testing • The loading and unloading frequency is irrelevant to at-speed testing • Slower frequency can be used to reduce power and constraints on test controller • Faster frequency can be used to reduce the test application time

Double capture first capture & transition launch last shift capture • Launch from a semi-legal state • Reduced overtesting • Double time frame sequential fault simulation Time frame 1 Time frame 2 Clk Sen

“Slow” scan enable clock scan enable last shift capture capture first shift Scan enable signal has 1.5 cycle to propagate Clock suppression Clock suppression Clk Sen

Slow scan enable Clock suppression Clock suppression Clk Sen Loading of random state last shift launch capture first shift

Slow scan enable Clock suppression Clock suppression Clk Sen 1. Initialization of internal nodes 2. Deactivation of scan enable 3. Propagation of scan enable signal (1.5 cycle) 4. Transition to a semi-legal state 5. Launch of transitions last shift launch capture first shift

Slow scan enable Clock suppression Clock suppression Clk Sen 1. Propagation of signals 2. Capture of responses last shift launch capture first shift

Slow scan enable Clock suppression Clock suppression Clk Sen 1. Activation of scan enable 2. Propagation of scan enable 3. First shift out of responses last shift launch capture first shift

Slow scan enable Clock suppression Clock suppression Clk Sen Continued unloading of responses last shift launch capture first shift

Phase lock loop circuit Frequency synthesis fp= nfclk Clock PLL fp / n

PLL deskewing PLL1 Clock PLL2 Deskewing No Yes global skew

Clock skew and race conditions clock • Clock skew results in race • Separate capture required

Fundamental principle Shift or capture Capture • If clock skew is not managed between A and B • If there is logic driven by A and captured in B • There should be no simultaneous change of state in A and capture in B Domain A Domain B

Multiple clock domains Objective: at-speed testing of logic within every clock domain and between clock domains BIST mode SE CLK SE CLK SE CLK PLL Test mode

Implementation - clock suppressed Clock suppression Clock suppression Clock suppression Clock suppression Clock suppression Clock suppression C S S* S* D1 C S S S* D2 C S S S D3 • Robust operations assured with clock skew between domains • Captured and shifted data used as a stimuli for other domains • The order of capture can change in different vectors • Combinational fault simulation is sufficient as the response data is shifted out • One scan enable signal can be used for all domains

Implementation with hold states H H H H H H Control H SE scan CLK C S S* S* D1 C S S S* D2 C S S S D3 • Clock suppression replaced with hold state • Non-capturing domains put in hold state

Multiple frequencies - single capture Load / unload window Capture window Clk1 C Clk1* Sen1 C Clk2* Sen2 • All intra and inter domain logic is tested at speed • Combinational fault simulation is adequate

Slow enable and multiple frequencies Clk1 C C Clk1* Sen1 C Clk2* Sen2

Multiple clock domains C S S D1 C S C S D2 S C S D3 • Multiple clocks per capture cycle • All inter domain logic can be tested • Sequential fault simulation

Multiple clock domains – domain analysis C C C C S S D1 C C S S D2 S D3 S • Merging non-interacting clock domains • Allows several clocks to be targeted at once • Reduces tester clock requirements • More efficient patterns • Better pattern count

Clock routing M I S R P R P G clock signals feeding “BIST ready” netlist Clock Control Sin BIST clock Sout Sen Scan ... ... Sen Scan PLL Shift counter BIST Run BIST Done hold Pattern counter External clock source BIST Reset

Embedded clock control clk1 - fastest PLL output Inputsfrom PLL Capture waveform generator for clk1 clk1 - out Capture waveform generator for clk2 clk2 - out Capture waveform generator for clk3 clk3 - out BIST Run Capture window Shift clock generator (Clock divider) BIST clock

Summary • Handling of multiple frequency and clock domains • Handling of very high speed designs with on-chip clocks • At-speed test in every inter- and intra-clock domain • Robust handling of clock skews through clock suppression and hold state • Separation of timing in loading-unloading and capture • No simultaneous change of state and capture in interacting domains without skew management • At-speed test is possible without at-speed scan • Power and ground bouncing can be managed by clock suppression and staggering in shift