Shift Register

DESCRIPTION

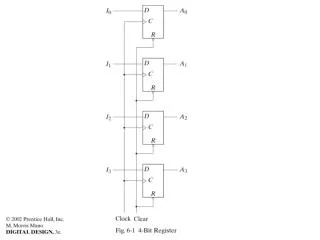

Shift Register. Section 6.1-6.2. In-Class Exercise. Load=“1”→Update. I 0 is fed to DFF when Load is a 1. “0”. “1”. “1”. “0”. “I 0 ”. “I 0 ”. Load=“0”→Hold!. A 0 is fed to DFF when Load is a 0. So the output is holding !. “1”. “0”. “0”. “A 0 ”. “A 0 ”. “0”.

1 / 8

Download Presentation

Shift Register

An Image/Link below is provided (as is) to download presentation

Download Policy: Content on the Website is provided to you AS IS for your information and personal use and may not be sold / licensed / shared on other websites without getting consent from its author.

Content is provided to you AS IS for your information and personal use only.

Download presentation by click this link.

While downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server.

During download, if you can't get a presentation, the file might be deleted by the publisher.

E N D

Presentation Transcript

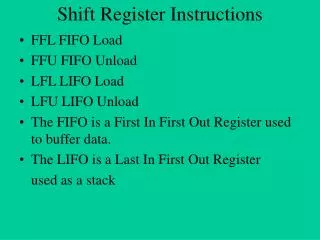

Shift Register Section 6.1-6.2

Load=“1”→Update I0 is fed to DFF when Load is a 1. “0” “1” “1” “0” “I0” “I0”

Load=“0”→Hold! A0 is fed to DFF when Load is a 0. So the output is holding! “1” “0” “0” “A0” “A0” “0” We will revisit this idea when we study the universal shift register.

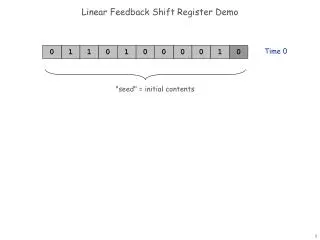

S0=0, S1=0 [No Change Mode] S0=0, S1=0

S0=1, S1=0 [Shift Right Mode] S1=0 , S0=1

S0=0, S1=1 [Shift Left Mode] S1=1 , S0=0

S0=1, S1=1 [Parallel Load Mode] S1=1 , S0=1

More Related