A MIPS R2000 Implementation

This project presents the implementation of a MIPS R2000 microarchitecture tailored for an introductory CMOS VLSI class aimed at undergraduates. Key features include a five-stage pipeline, hazard and exception units, a Booth-encoded radix-4 multiplier/divider, and integrated 512-byte instruction/data caches with a 4-entry write buffer. The design also encompasses project partitioning, RTL microarchitecture, FPGA emulation, schematics/layout in Electric, and custom PLA generation. Performance testing indicates the design operates at 7.25 MHz with a power consumption of 52 mW. More details can be found at the provided web link.

A MIPS R2000 Implementation

E N D

Presentation Transcript

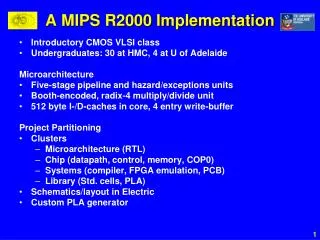

A MIPS R2000 Implementation • Introductory CMOS VLSI class • Undergraduates: 30 at HMC, 4 at U of Adelaide Microarchitecture • Five-stage pipeline and hazard/exceptions units • Booth-encoded, radix-4 multiply/divide unit • 512 byte I-/D-caches in core, 4 entry write-buffer Project Partitioning • Clusters • Microarchitecture (RTL) • Chip (datapath, control, memory, COP0) • Systems (compiler, FPGA emulation, PCB) • Library (Std. cells, PLA) • Schematics/layout in Electric • Custom PLA generator

Fabrication Verification • DRC/NCC/ERC in Electric • Ad-hoc Verilog behavioral • Random test vector generation • IRSIM switch-level simulations • Single-/dual-FPGA emulation Fabrication • CIF generated by Electric • AMI Mosis 0.5-mm, 4.5 mm • 160k transistors • 108-pin PGA

Testing/Performance Performance • 7.25 MHz, limited by caches • Power is 52 mW @ 7.25 MHz More Information • http://www4.hmc.edu:8001/Engineering/158/07/project