XESS XSV Board

80 likes | 240 Views

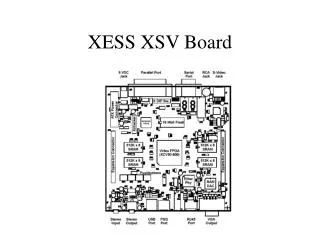

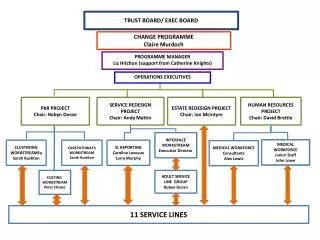

XESS XSV Board. ATX P.S. XESS XSV Board. J11. 48 MHz Clock. PC HIDtest Software driver to usbpads/Philips xcvr XSLOAD Loads configuration bitstream. Sw1. Philips xcvr. (rst) (clk) Xilinx FPGA XSV300. A. A. P P. P P. 95108 CPLD. HW Diagram.

XESS XSV Board

E N D

Presentation Transcript

ATX P.S. XESS XSV Board J11 48 MHz Clock PC HIDtest Software driver to usbpads/Philips xcvr XSLOAD Loads configuration bitstream Sw1 Philips xcvr (rst) (clk) Xilinx FPGA XSV300 A A P P P P 95108 CPLD HW Diagram

xsvPads.vhd (wrapper) clk (48 MHz) rst xsvCore.vhd din (16) @ 16 Mb/s xsvPHY. vhd usbMacro.edf (EDIF) Your design (xsvFunct.vhd) O P 1 I N S T R E G I N S T R E G I N S T R E G I N S T R E G I N S T R E G I N S T R E G I N S T R E G I N S T R E G urxd urxo utxd utxo utxoe O P 2 vm vp vmo vpo rcv oe suspnd dout (16) @ 16 Mb/s RISC VHDL Functional Diagram

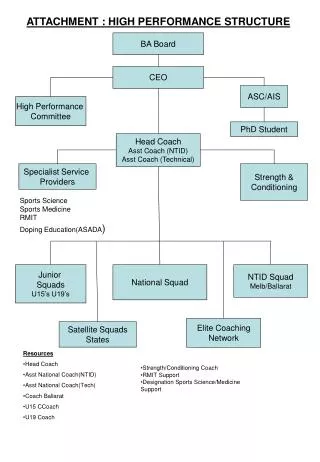

DATA INPUT/OUTPUT Instructions (Mult, Divide) USB PORT CONFIG FILE describing Processor VHDL Core VHDL CODE, UCF FILE XILINX ISE XSLOAD Parallel Port VIRTEX BOARD FPGA Configuration and Dataflow Processes

Host Software Operation, Referenced Files and Modified Project Information • Modified Project: • Integrate your RISC design into the embedded project by using xsvFunc.vhd as a wrapper for your design. • Synthesize xsvPads and implement (create a bit stream) using the given ucf and usbMacro EDIF files in Xilinx ISE Alliance. • Download configuration file bitstream into XSV board using XSTOOLs (E218) • Using hidTest on the PC (in E218), write the 32-bit instructions followed by two 16-bit multiplicands (the upper byte of each is 0x00) and read the 16-bit result kahuna.sdsu.edu/~harris Website will have links to: • VHDL • Macro (EDIF; > 1MB) • ucf File • Host Controller S/W Source Code • XSV Manual, Trenz USB, SIE, M51 pdf’s