Sequential design

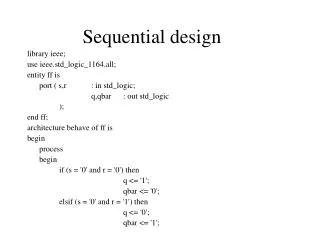

Sequential design. library ieee; use ieee.std_logic_1164.all; entity ff is port ( s,r : in std_logic; q,qbar : out std_logic ); end ff; architecture behave of ff is begin process begin if (s = '0' and r = '0') then q <= '1'; qbar <= '0';

Sequential design

E N D

Presentation Transcript

Sequential design library ieee; use ieee.std_logic_1164.all; entity ff is port ( s,r : in std_logic; q,qbar : out std_logic ); end ff; architecture behave of ff is begin process begin if (s = '0' and r = '0') then q <= '1'; qbar <= '0'; elsif (s = '0' and r = '1') then q <= '0'; qbar <= '1';

elsif (s = '1' and r = '0') then q <= '1'; qbar <= '0'; else q <= '0'; qbar <= '0'; end if; end process; end behave;

D-flip flop library ieee; use ieee.std_logic_1164.all; entity dff is port (d, clk : in std_logic; q, qbar : out std_logic ); end dff;

architecture behave of dff is signal temp : std_logic; begin process (clk) begin if (clk'event and clk = '0') then temp <= d; end if; q <= temp; qbar <= not temp; end process; end behave;

SR flip-flop (process) library ieee; use ieee.std_logic_1164.all; entity ffclk is port ( s,r,clk : in std_logic; q,qbar : out std_logic ); end ffclk;

architecture behave of ffclk is signal temp,tempbar : std_logic; begin process (clk) begin if (clk = '1') then if (s = '0' and r = '0') then temp <= '1'; tempbar <= '0'; elsif (s = '0' and r = '1') then temp <= '0'; tempbar <= '1';

elsif (s = '1' and r = '0') then temp <= '1'; tempbar <= '0'; else temp <= '0'; tempbar <= '0'; end if; else temp <= temp; tempbar <= tempbar; end if; q <= temp; qbar <= tempbar; end process; --q <= temp; --qbar <= tempbar; end behave;

counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity counter4bit is port (load,clear, clk : in std_logic; d : in std_logic_vector (3 downto 0); q : out std_logic_vector (3 downto 0) ); end counter4bit;

architecture behave of counter4bit is signal temp : std_logic_vector (3 downto 0); begin a: process (clk,load,clear,d) begin if (load = '1') then temp <= d; elsif (clear = '1') then temp <= "0000"; elsif (clk'event and clk = '1') then temp <= temp + "0001"; else

temp <= temp; end if; end process a; q <= temp; --b: process (clk) --begin --if (clk'event and clk = '1') then --q <= temp; --end if; --end process b; end behave;