ARM Cortex-M0

E N D

Presentation Transcript

ARM Cortex-M0 CORTEX-M0 StructureDiscussion 2 – Core Peripherals August 22, 2012Paul NickelsbergOrchid Technologies Engineering and Consulting, Inc.www.orchid-tech.com

Cortex-M0 StructureDiscussion 2 – Core Peripherals Topics Today • CORTEX-M0 SYSTICK Core Peripheral • CORTEX-M0 NVIC Core Peripheral • CORTEX-M0 SCB Core Peripheral

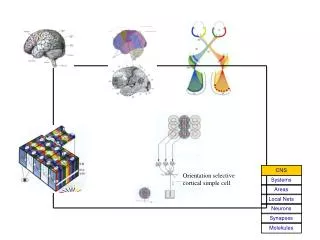

Cortex-M0 Core Peripherals Cortex-M0 32 Bit CPU SYSTICK NVIC SCB Core Peripherals are Common to All Cortex Devices

SYSTICK Core Peripheral Cortex-M0 CPU System Clock SysTick Interrupt 24-Bit Reload Register IRQ Control Register 24-Bit Down Counter

SYSTICK Core Peripheral P e r i o d i c I n t e r r u p t s time Time interval = Reload Count / Clock Frequency

SYSTICK Core Peripheral • Simple Periodic Interval Timer • Identical Structure in Cortex-M0, M3, M4 • Settable Interrupt Priority • 24-Bit Counter Width • Count Enable Control • Interrupt Enable Control

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is an Interrupt Controller? INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION Normal Program FlowInstruction Proceed in Sequence

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is an Interrupt Controller? INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION Interrupt Event Normal Program Flow Interrupt Service Program Flow Interrupt Return

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is an Interrupt Controller? • An Interrupt Controller manages the process of interrupting normal program flow upon receipt of an interrupt event • Interrupt Entry: • Push Stack Frame • Fetch Interrupt Vector • Interrupt Exit: • Pop Stack Frame • Resume normal program execution

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Vectored’ Interrupt Controller? Vector Table contains Start Address of InterruptService Routine Vector Table InterruptController Interrupt Service Routine 2 VECTOR 0 VECTOR 1 VECTOR 2 VECTOR 3 VECTOR 4 VECTOR 5 VECTOR 6 VECTOR 7 VECTOR 8 VECTOR N Interrupt Service Routine 8 Individual Interrupts Interrupt Service Routine 4 Interrupt Service Routine 6

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Vectored’ Interrupt Controller? • An Interrupt Vector is a unique 32-Bit value which is set to the Start Address of an Interrupt Service Routine • Interrupt Vectors are Stored in a Sequential Table of Vectors • Vectored Interrupts have low latency

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Vectored’ Interrupt Controller?

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Vectored’ Interrupt Controller? NOT VECTORED VECTORED Normal Program Flow Normal Program Flow Has extra stepslonger latency Receive Interrupt Receive Interrupt Branch to Global Service Routine Service Unique Interrupt Service Unique Interrupt Determine Unique Interrupt Return to Normal Program Flow Return to Normal Program Flow Older ARM7 Style New CORTEX Style

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller? Low Priority High Priority INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION Interrupt Event Interrupt Event Normal Program Flow Interrupt Service Program Flow Interrupt Service Program Flow Interrupt Return Interrupt Return

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller? Nested Interrupt Support • Individual Interrupts have Priority • Higher Priority Interrupt will Preempt Lower • Lower or Equal Priority Interrupt will Wait • Interrupt Tail Chaining to Reduce Latency • Interrupt Late Arriving to Reduce Latency

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller?

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller?

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller? Int Pop Stack Frame Service Interrupt Push Stack Frame Normal program flow Normal program flow Int 1 Int 2 Service Interrupt 1 Service Interrupt 2 Service Interrupt 1 Push Stack Frame 2 Pop Stack Frame 2 Pop Stack Frame 1 Push Stack Frame 1 Normal program flow Normal program flow Interrupt Preemption – Int 2 Higher Priority Than Int 1

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller? Int Pop Stack Frame Service Interrupt Push Stack Frame Normal program flow Normal program flow Int 1 Int 2 Service Interrupt 2 Pop Stack Frame Service Interrupt 1 Push Stack Frame Normal program flow Normal program flow Interrupt Tail Chaining – Int 1 Higher or Equal Priority Than Int 2

Nested-Vectored Interrupt ControllerNVIC Core Peripheral What is a ‘Nested’ Vectored Interrupt Controller? Int Pop Stack Frame Service Interrupt Push Stack Frame Normal program flow Normal program flow Int 1 Int 2 Service Interrupt 1 Pop Stack Frame Service Interrupt 2 Push Stack Frame Normal program flow Normal program flow Interrupt Late Arriving – Int 2 Higher Priority Than Int 1

SCB Core Peripheral • Register Set which provides system implementation and system control functions • CPU ID Register • Interrupt Control and State Register • Application Interrupt and Reset Control Register • System Control Register • Configuration Control Register • System Handler Priority Registers

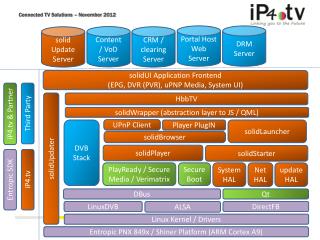

Cortex-M0+ PeripheralMPC Core Peripheral Memory Protection Unit • CORTEX-M0+ Eight Separate Regions • CORTEX-M0+ Overlapping Regions • CORTEX-M0+ Background Regions

Meaning and Implications 32 Bit CORTEX-M0 Processing Capability Sophisticated NVIC Interrupt Control Low Latency Interrupt Features Vectoring, Preemption, Chaining, Late Arrival Core Control Features Memory Protection Unit 8 Bit Architecture Processor Architecture – 8 Bit World to 32 Bit World