PROGRAMABILNI PERIFERIJSKI INTERFEJS INTEL 8255

PROGRAMABILNI PERIFERIJSKI INTERFEJS INTEL 8255. Studenti: Alen Eftimov 8736 Dragan Živković 8737. SERIJSKI I PARALELNI PRENOS PODATAKA. Postoje dva tipa prenosa podataka:

PROGRAMABILNI PERIFERIJSKI INTERFEJS INTEL 8255

E N D

Presentation Transcript

PROGRAMABILNI PERIFERIJSKI INTERFEJSINTEL 8255 Studenti: Alen Eftimov 8736 Dragan Živković 8737

SERIJSKI I PARALELNIPRENOS PODATAKA Postoje dva tipa prenosa podataka: 1)Serijski – preko jedinstvene veze (žice),ili komunikacionog kanala,a u datom trenutku se prenosi po jedan bit. 2)Paralelni – preko većeg broja veza (žica),u datom trenutku se prenosi više bitova.

SERIJSKIPRENOS PODATAKA • Serijska informacija se prenosi preko jedinstvene linije na principu bit-po-bit. • Smanjuje se broj veza(žica) kojim se CPU povezuje sa U/I uređajem. • Karakteriše ga niža cena i veća pouzdanost (lakša detekcija greške). • Serijski prenos je sporiji. • Koristi za prenos na većim rastojanjima.

PARALELNIPRENOS PODATAKA • Posebnim linijama prenosi se veći broj bitova. • Dobijamo veću brzinu prenosa, veću nepouzdanost prenosa , težu detekciju greške i veću cenu. • Koristese za kraća rastojanja. • Za razliku od serijskih, nisu dobro standardizovane.

Povezivanje izlaznog interfejsa na izlazni uređaj tipa D/A konvertor zasnovan na paralelnom prenosu

Primer paralelnog interfejsa kod koga se koriste handshake upravljačke linije

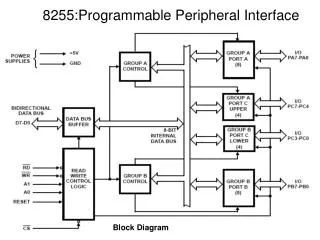

PROGRAMABILNI PERIFERIJSKI INTERFEJS(PPI)INTEL 8255 • 8255 je programabilni čip opšte namene projektovan za upotrebu u mikroprocesorskim sistemima • Njegova funkcija je U/I komponenta opšte namene za povezivanje periferijske opreme na 8080 sistemsku magistralu • Funkcionalna konfiguracija kola 8255 je programirana sistemskim softverom tako da nije potrebna spoljašnja logika za povezivanje periferijskih uređaja ili struktura.

Ima 40 pina od kojih se 24 ulazno-izlazna pina mogu pojedinačno programirati u dve grupe od dvanaest pinova

Ovaj čip koristi se u tri osnovna režima rada: • Mode 0 (Režim 0) - svaka grupa od dvanaest ulazno-izlaznih pinova može da se programira u skupove od po 4, koji mogu da budu ulazi ili izlazi • Mode 1(Režim 1) - svaka grupa može da se programira da ima 8 linija ulaza ili izlaza. Od preostalih četiri, tri pina se koriste za signale handshake protokola i kontrolu prekida • Mode 2(Režim 2) - predstavlja dvosmerni rad magistrale koja koristi 8 linija za dvosmernu magistralu, i pet linija, pozajmljujući jednu od ostalih grupa, za handshake protokol

Bafer magistrale podataka - osmobitni bafer koji se koristi za povezivanje 8255 na sistemsku magistralu podataka procesora 8080 Čitanje/upis i kontrolna logika - funkcija ovog bloka je da upravlja svim unutrašnjim ili spoljašnjim prenosima podataka, statusnih ili kontrolnih rečiOn prihvata ulaze sa adresa procesora 8080 i kontrolnih magistrala, i po redu izdaje komande obema kontrolnim grupama. • (nCS) - Chip Select (selektovanje čipa): “nizak nivo” na ovom ulaznom pinu omogućava komunikaciju između ‚čipa 8255 i procesora. • (nRD) - Read (čitanje): “nizak nivo” na ovom ulaznom pinu omogućava čipu 8255 da pošalje podatke i statusne informacije procesora na magistralu podataka. U suštini, omogućava da procesor pročita podatke iz 8255. • (nWR) - Write (upis): “nizak nivo” na ovom ulaznom pinu omogućava procesoru da upisuje podatke i kontrolne reči u čip 8255.

(A0 i A1) - Selekcija Portova 0 i 1: Ovi ulazni signali, u vezi sa i ulazima, kontrolišu izbor jednog od tri porta za registar kontrolne reči. Oni su normalno povezani na najmanje značajne bitove adresne magistrale (A0 i A1). (RESET) -Reset: “visok nivo” na ovom ulazu briše sve unutrašnje registre uključujući i kontrolni registar i svi Portovi (A, B i C) se postavljaju u ulazni režim.

Kontrolne grupe A i B - Svaki od kontrolnih blokova (grupa A i grupa B) prihvataju komande od kontrolne logike, prihvataju kontrolne reči od unutrašnje magistrale podataka i izdaju odgovarajuće komande njima dodeljenim portovima. • Kontrolna grupa A ( Port A i viši C port (C7-C4)) • Kontrolna grupa B ( Port B i niži C port (C3-C0)) Portovi A, B i C– 8 bitni portovi. Svi oni se mogu konfigurisati sistemskim softverom • Port A: jedan 8-bitni izlazni leč/bafer i jedan 8-bitni ulazni leč. • Port B: jedan 8-bitni ulazno/izlazni leč/bafer i jedan 8-bitni ulazni bafer. • Port C: jedan 8-bitni izlazni leč/bafer i jedan 8-bitni ulazni bafer (nema leča na ulazu). Ovaj port može se podeliti na dva 4-bitna porta u zavisnosti od režima.

Izbor režima rada Režima rada se mogu selektovati sistemskim softverom: • Režim 0 – Osnovni Ulaz/Izlaz • Režim 1 - Prekidni Ulaz/Izlaz • Režim 2 – Dvosmerna magistrala

Režimi za portove A i B mogu se odvojeno definisati, dok se Port C deli na dva dela • Režimi se mogu kombinovati tako da se njihova funkcionalna definicija može prilagoditi bilo kojoj U/I strukturi Na primer : Grupa B se može programirati u Režimu 0 da nadgleda jednostavna zatvaranja prekidača ili da prikaže rezultate izračunvanja. Grupa A se može programirati u Režimu 1 da nadgleda tastaturu ili čitač trake na osnovu prekida.

Režim 0 ( osnovni ulaz/izlaz ) • Ova funkcionalna konfiguracija obezbeđuje jednostavne ulazne i izlazne operacije za svaki od tri porta • Ne zahteva se handshaking protokol, već se podaci jednostavno upisuju ili čitaju sa zadatog porta • Kada se Port C koristi kao status / kontrola za port A ili B, ovi bitovi se mogu setovati ili resetovati bitskim operacijama kao da su izlazni portovi podataka

Osnovne funkcionalne definicije Režima 0 • Dva 8-bitna i dva 4-bitna porta • Svaki port može biti ulazni i izlazni • Izlazi su lečovani • Ulazi nisu lečovani • U ovom režimu su moguće 16 različitih ulazno/izlaznih konfiguracija

Režim 1 ( prekidni ulaz/izlaz ) • Obezbeđuje prenos U/I podataka ka i od zadatog porta u vezi sa signalima prekida ili handsaking protokola • Portovi A i B koriste linije na Portu C da generišu ili prihvate signale handshaking protokola

Osnovne funkcionalne definicije Režima 1 • Dve grupe (grupa A i grupa B) • Svaka grupa sadrži jedan 8-bitni port podataka i jedan 4-bitni kontrolni ili port podataka • 8-bitni port podatka može biti ili ulazni ili izlazni. I ulazi i izlazi su lečovani. • 4-bitni port se koristi za kontrolu i status 8-bitnog porta podataka.

nSTB - strobe ulaz • IBF - ulazni bafer pun (Jedinica na ovom izlazu ukazuje da su podaci upisani u ulazni leč. U suštini, ovo je potvrda. IBF se setuje kada je STB ulaz na nuli, a resetuje se tokom rastuće ivice ulaza) • INTR- zahtev za prekid (Jedinica na ovom izlazu se može iskorititi da prekida processor kada ulazni uređaj zahteva opsluživanje. INTR se setuje kada je nSTB na jedinici, IBF je na jedinici i INTE je na jedinici. Resetuje se tokom opadajuće ivice nRD. Ova procedura omogućava ulaznim uređajima da zahtevaju opsluživanje od procesora jednostavnim izbacivanjem podataka na port) • INTE A- kontrolisan bitskim setovanjem/resetovanjem PC4 • INTE B - kontrolisan bitskim setovanjem/resetovanjem PC2

nOBF - izlazni bfer pun (Izlaz nOBF će se postaviti na nulu da ukaže da je processor upisao podatke na zadati port. OBF F/F će se setovati rastućom ivicom WR ulaza i resetovati kada je ulaz nACK na nuli) • nACK - ulaz potvrde (Nula na ovom ulazu informiše 8255 da su podaci sa Portova A i B prihvaćeni. U suštini, odgovor sa periferijskog uređaja ukazuje da je primio podatke sa izlaza CPU) • INTR - zahtev za prekid (Jedinica na ovom izlazu može se upotrebiti da prekida CPU kada je izlazni uređaj primio podatke (prenete sa procesora). INTR se setuje kada je nACK na jedinici, nOBF je na jedinici i INTE je na jedinici. Resetuje se tokom opadajuće ivice nWR)

Režim 2 ( Prekidna dvosmerna U/I magistrala ) • Ova funkcionalna konfiguracija obezbeđuje značaj za komunikaciju sa periferijskim uređajem ili strukturom preko jedne 8-bitne magistrale i za predaju i za prijem podataka (dvosmerna U/I magistrala) • Signali handshaking protokola koriste se da održe propisan protok magistrale na sličan način kao kod Režima 1 • Dostupne su funkcije generisanja i dozvole/zabrane prekida

Osnovne funkcionalne definicije Režima 2 • Koristi se samo u grupi A • Jedan 8-bitni, dvosmerni port (Port A) i 5-bitni kontrolni port (Port C) • I ulazi i izlazu su lečovani • 5-bitni kontrolni port (Port C) se koristi za kontrolu i status 8-bitnog, dvosmernog porta (Port A)

INTR - zahtev za prekid Izlazne operacije: • nOBF - izlazni bafer pun • nACK – potvrda • INTE 1 (INTE flip-flop dodeljen sa nOBF ) Ulazne operacije: • nSTB - strobe ulaz • IBF - ulazni bafer pun • INTE 2 (INTE flip-flop dodeljen sa IBF)

Sprega 8255 sa čitačem kartica i industijskim mikrokontrolerom

U strukturi razlikujemo 9 entiteta, odnosno blokova: • Ctrl_log • PortAin • PortBin • DoutMUX • PortAout • PortBout • PortCout • CLK_gen • MUX_global

Bilo kakav transport podataka unutar ili van čipa 8255 odvija se na osnovu kontrolnih i upravljačkih signala koje generiše ovaj entitet (blok) ENTITET: Ctrl_log

ENTITY Ctrl_log IS PORT( Reset : IN std_logic; Clk : IN std_logic; nCS : IN std_logic; nRD : IN std_logic; nWR : IN std_logic; A : IN std_logic_vector (1 DOWNTO 0); Din : IN std_logic_vector (7 DOWNTO 0); Cin : IN std_logic_vector (7 DOWNTO 0); Aen : OUT std_logic; Ben : OUT std_logic; Cen : OUT std_logic_vector (7 DOWNTO 0); DoutSelect : OUT std_logic_vector (2 DOWNTO 0); CtrlReg : OUT std_logic_vector (7 DOWNTO 0); Ard : OUT std_logic; Brd : OUT std_logic; Awr : OUT std_logic; Bwr : OUT std_logic; AoutLd : OUT std_logic; BoutLd : OUT std_logic; Coverride : OUT std_logic; CoutLd : OUT std_logic_vector (7 DOWNTO 0) ); END Ctrl_log; OPIS ENTITETACtrl_log:

SIGNAL CtrlRegD : std_logic_vector(6 DOWNTO 0); -- Lecovano stanje Kontrolnog R SIGNAL CtrlRegQ : std_logic_vector(6 DOWNTO 0); -- Upisano stanje Kontrolnog Registra SIGNAL ModeA : std_logic_vector(1 DOWNTO 0); -- Mod Registra A SIGNAL ModeB : std_logic; -- Mod Registra B SIGNAL PortA_IO : std_logic; -- Registar A je ulazni/izlazni SIGNAL PortB_IO : std_logic; -- Registar B je ulazni/izlazni SIGNAL PortCUp_IO : std_logic; -- Kontrola viseg dela Registra C SIGNAL PortCLow_IO : std_logic; -- Kontrola nizeg dela Registra C SIGNAL CtrlRegWrite : std_logic; -- Dozvola upisa stanja u Kontrolni Registar Komponenta Ctrl_log upravlja radom cipa 8255. Ovaj blok generise svaki interni upravljacki signal Signali u koji opisuju arhitekturu Ctrl_log su: OPIS ARHITEKTURE: Ctrl_log

Svaki bit kontrolnog registra predstavlja nekiupravljacki bit za registre A,B i C. Poslednji bit kontrolnog registra je uvek '1‘, u suprotnom komandnim registrom se setuje/resetuje registar C Sada cemopopuniti komandni bajt Komandnog registra OPIS ARHITEKTURE: Ctrl_log- nastavak CtrlReg <= '1' & CtrlRegQ; ModeA <= CtrlRegQ (6 DOWNTO 5); ModeB <= CtrlRegQ (2); PortA_IO <= CtrlRegQ (4); PortB_IO <= CtrlRegQ (1); PortCUp_IO <= CtrlRegQ (3); PortCLow_IO <= CtrlRegQ (0); Generisanje informacije o prekoracenju, tj.kada procesor "puni" Kontrolni Registar IF (nCS = '0' AND A = "11" AND Din(7) = '0') THEN Coverride <= '1'; ELSE Coverride <= '0'; END IF;

OPIS ARHITEKTURE: Ctrl_log - nastavak -- Nacin generisanja dozvole portu Aout: AoutLd <= '0' WHEN nCS = '0' AND A = "00" AND nWR = '0' ELSE '1'; -- Nacin generisanja dozvole portu Bout: BoutLd <= '0' WHEN nCS = '0' AND A = "01" AND nWR = '0' ELSE '1'; -- Od vrednosti A (koju salje procesor) Ctrl_log daje naredbu DoutMUX-u koji signal da propusti na svom izlazu: CASE A IS WHEN "00" => -- Port A IF (ModeA = "00") THEN -- Ukoliko je Port A u Modu 0 DoutSelect <= "000"; -- Selektuje se nelecovani podatak PAin ELSE DoutSelect <= "001"; -- U suprotnom, selektuje se lecovani podatak PAin. END IF; WHEN "01" => -- Port B IF (ModeB = '0') THEN -- Ukoliko je Port B u Modu 0 DoutSelect <= "010"; -- Selektuje se nelecovani podatak PBin ELSE DoutSelect <= "011"; -- U suprotnom, selektuje se lecovani podatak PBin. END IF; WHEN "10" => -- Port C DoutSelect <= "100"; -- Selekcija podatka Cin WHEN "11" => DoutSelect <= "110"; -- Selekcija podatka iz Kontrolnog Registra WHEN OTHERS => NULL; END CASE;

ENTITET: PortAin Realizacija Porta A je efikasnija ukoliko se on podeli na ulazni i izlazni deo. Ulazni segment porta sadrži logiku koja prihvata podatke. PortAin prihvata podatke iz «spoljnjeg sveta» preko globalnog multipleksera, a prosleđuje ih prema entitetu DoutMux

ENTITY PortAin IS PORT( Ain : IN std_logic_vector (7 DOWNTO 0); AInReg : OUT std_logic_vector (7 DOWNTO 0); Reset : IN std_logic; Clk : IN std_logic; AInLd : IN std_logic ); END PortAin; OPIS ENTITETA:PortAin

OPIS ARHITEKTURE: PortAin ARCHITECTURE rtl OF PortAin IS --Definisanje internih signala unutar ulaznog delaPorta A (Ain) SIGNAL AinRegQ : std_logic_vector(7 DOWNTO 0); SIGNAL AinRegD : std_logic_vector(7 DOWNTO 0); BEGIN AinReg <= AinRegQ; --Ulazni deo Porta A (Ain) mozemo smatrati kaosistem 2 x 8 latch-eva "pojacan" sa dodatnom logikom AinProc1: PROCESS ( AinLd, Ain, AinRegQ ) BEGIN --Kada je aktivan signal AinLd, azurira se sadrzajPorta Ain, 8-bitnim podatkom koji je na njegovomulazu IF ( AinLd = '0') THEN AinRegD <= Ain (7 DOWNTO 0); ELSE AinRegD <= AinRegQ; END IF; END PROCESS; AinProc2: PROCESS ( Reset, Clk ) BEGIN --Ukoliko je prisutan spoljasnji Reset, stanje Porta Ainpostaje "00000000" IF (RESET = '1') THEN AinRegQ <= "00000000"; --Sa usponskom ivicom takta 8-bitni podatak ce bitidostupan na izlazu ELSIF ( Clk'EVENT and Clk = '1') THEN AinRegQ <= AinRegD; END IF; END PROCESS; END rtl;

Realizacija Porta B je efikasnija ukoliko se on podeli na ulazni i izlazni deo. PortBin prihvata podatke preko iz «spoljnjeg sveta» preko globalnog multipleksera, a prosleđuje ih prema entitetu DoutMux. Naravno, da li će se Port B ponašati kao ulazni ili kao izlazni, zavisi od upravljačkih signala, koja sa procesora dolazi na entitet (blok) Cnt_log. ENTITET: PortBin

ENTITY PortBin IS PORT( Reset : IN std_logic; Clk : IN std_logic; Bin : IN std_logic_vector (7 DOWNTO 0); BinLd : IN std_logic; BinReg : OUT std_logic_vector (7 DOWNTO 0) ); END PortBin; OPIS ENTITETA:PortBin

OPIS ARHITEKTURE: PortBin ARCHITECTURE rtl OF PortBin IS -- Definisanje internih signala unutar ulaznog dela Porta B (Bin) SIGNAL BinRegQ : std_logic_vector(7 DOWNTO 0); SIGNAL BinRegD : std_logic_vector(7 DOWNTO 0); BEGIN BinReg <= BinRegQ; BinProc1: PROCESS ( BinLd, Bin, BinRegQ ) -- Ulazni deo Porta B (Bin) mozemo smatrati kao sistem 2 x 8 latch-eva sa dodatnom logikom; BEGIN -- Kada je aktivan signal BinLd (ovaj signal generise blok Ctrl_log) upisuje se sadrzaj sa ulaza Porta Bin IF ( BinLd = '0') THEN BinRegD <= Bin (7 DOWNTO 0); ELSE BinRegD <= BinRegQ; END IF; END PROCESS; BinProc2: PROCESS ( Reset, Clk ) BEGIN -- Kada je prisutan spoljasnji Reset, stanje Porta Bin se anulira, tj. postaje "00000000". Onog trenutka kada naidje usponska ivica takta, sadrzaj Porta Bin se prenosi na izlaz BinReg IF (Reset = '1') THEN BinRegQ <= "00000000"; ELSIF ( Clk'EVENT and Clk = '1') THEN BinRegQ <= BinRegD; END IF; END PROCESS; END rtl;

Zadatak entiteta DoutMux je da na osnovu upravljačkih signala generisanih od strane entiteta Cnt_log, definiše transport podataka prema izlaznim segmentima portova A, B i C (PortAout, PortBout, PortCout) ENTITET: DoutMUX