Agenda

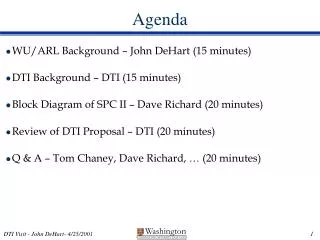

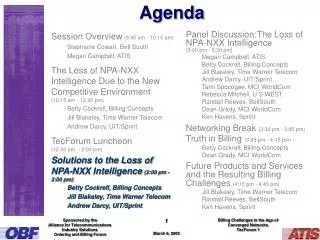

Agenda. WU/ARL Background – John DeHart (15 minutes) DTI Background – DTI (15 minutes) Block Diagram of SPC II – Dave Richard (20 minutes) Review of DTI Proposal – DTI (20 minutes) Q & A – Tom Chaney, Dave Richard, … (20 minutes).

Agenda

E N D

Presentation Transcript

Agenda • WU/ARL Background – John DeHart (15 minutes) • DTI Background – DTI (15 minutes) • Block Diagram of SPC II – Dave Richard (20 minutes) • Review of DTI Proposal – DTI (20 minutes) • Q & A – Tom Chaney, Dave Richard, … (20 minutes)

Washington UniversityApplied Research Laboratoryand theWU Active RouterJohn DeHartWashington University, Applied Research Labhttp://www.arl.wustl.edu/arl/

Applied Research Laboratory • Licensed Technology • ATM Switch (SynOptics) • MMX (STS: local startup) • ATM Software (3-4 companies) • ATM Circuits/Designs (GNI) • … • Current Staff • 2 Full time faculty • 1 Research faculty • 3 Part time faculty • 10 Full time staff • About 20 students • Current Projects • WUGS 160 • Burst Switch • Multi-Service Router • Active Network Node • Network Monitoring Visualization and Control • Gigabit Network Technology Distribution Program • …

Washington University Active Router ControlProcessor Smart Port Card Switch Fabric 64 MB Sys.FPGA APIC NorthBridge IPP OPP IPP OPP IPP OPP IPP OPP IPP OPP IPP OPP Pentium SPC SPC SPC SPC SPC SPC Cache Input Port Processor TI TI TI TI TI TI VCI VCI OUT • Control Processor • global coordination & control • routing protocols • build routing tables and other information needed by SPCsand FPXs • first level code server

Cell Processing Input Port Processor ControlProcessor Switch Fabric 3 6 5 6 5 IPP OPP IPP OPP IPP OPP IPP OPP IPP OPP IPP OPP SPC SPC SPC SPC SPC SPC TI TI TI TI TI TI 3 6

Active Packet Processing ControlProcessor Switch Fabric 6 6 5 5 6 5 IPP OPP IPP OPP IPP OPP IPP OPP IPP OPP IPP OPP Smart Port Card Pentium 32-64 MB Sys.FPGA SPC SPC SPC SPC SPC SPC Cache APIC NorthBridge TI TI TI TI TI TI 6 3 3 6 6 3

Principal Data Flows Through SPC Kernel HW Interrupt Context SW Interrupt Context HW Interrupt Context PacketClassificationand Routing IPv4/6HeaderProcessing Packet +Flow Id Plain Packets IP Packets Kernel Plugins Active Packets . . . ActiveFunctionDispatcher Driver PacketScheduler Driver . . . . . . • Standard processing for “plain” IP packets. • classification and routing, header processing, output queueing • Active packets move through configured kernel plugins. • active function dispatcher passes packets to instances of plugin objects • instantiates objects or triggers download of plugin class, as needed

User SW Interrupt Kernel PSN PS2 PS1 X.1 Z.1 Y.1 ANN Kernel SW Interrupt akintr SPC IP options W.1 X.2 Y.1 Z.2 AN Framework Input 1 Active Processing Standard IP Processing Input 2 Default Input port path PSout To CP ... H APIC M Packet schedulers Basic IP Processing (TTL, version, addr, options chk) Exact Match Classifier L ... Manage Queues and Memory Input N H H H H H M M M M M L L L L L ... interrupt Output 2 Output 1 Next Hop Output N Default Output path to Next Hop Prev Hop APIC Driver APIC MSR: h Phase 1.0

Input Port Forwarding Rate Packet size == 1 Cell 250 600 MHz PIII 200 150 200 MHz PPro Forwarded Rate (Kpps) 100 50 0 0 50 100 150 200 250 300 Input Rate (Kpps)

Hardware Support for Active Routing ControlProcessor Field Programmable Port Ext. Smart Port Card SDRAM128 MB SRAM4 MB Switch Fabric 64 MB Sys.FPGA APIC NorthBridge IPP OPP IPP IPP IPP IPP OPP OPP OPP OPP IPP OPP Pentium FPX FPX FPX FPX FPX FPX Cache SPC SPC SPC SPC SPC SPC ReprogrammableApplicationDevice NetworkInterfaceDevice TI TI TI TI TI TI

“Vanilla” IP Packet Processing ControlProcessor Field Programmable Port Ext. Switch Fabric 6 6 5 5 6 5 Field Programmable Port Ext. RAD NID IPP OPP IPP IPP IPP IPP OPP OPP OPP OPP IPP OPP RAD FPX FPX FPX FPX FPX FPX NID SPC SPC SPC SPC SPC SPC TI TI TI TI TI TI 3 6 3 6 3 6

Active Packet Processing ControlProcessor Field Programmable Port Ext. Switch Fabric 6 6 5 5 6 5 RAD NID IPP OPP IPP IPP IPP IPP OPP OPP OPP OPP IPP OPP Smart Port Card Pentium 32-64 MB Sys.FPGA FPX FPX FPX FPX FPX FPX Cache APIC NorthBridge SPC SPC SPC SPC SPC SPC TI TI TI TI TI TI 3 6 6 3 6 3

Sample Applications • Application Specific Congestion Control • Video: dropping high frequency portions of image first • Application specific • Small fixed portion of payload gets processed • Reserved Flow Setup • Low overhead soft-state bandwidth reservations • Application independent • Header processing only • Networked Vision • Image processing in the network, close to the camera • Application specific • Possibly full payload processing

Active Congestion Control for Video • Based on wavelet-based encoding method (WaveVideo) • up to hundreds of distinct frequency subbands (33) • low frequencies: general image definition • high frequencies: image details • Active WaveVideo plugin • detects congestion • discards packets in high frequency subbands first • Better performance than layered multicast • requires large number of multicast groups • reacts too slowly to congestion ( several seconds)

WaveVideo Scaling 33011 bytes (33) 25239 bytes (30) 17179 bytes (27) 9265 bytes (24) 7042 bytes (21) 4819 bytes (18) 2617 bytes (15) 2006 bytes (12) 1393 bytes (9) 793 bytes (6) 447 bytes (3) 227 bytes (1)