Brief Hardware Status

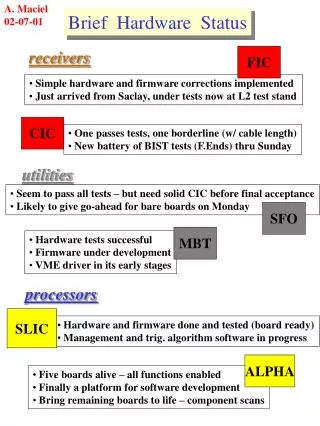

A. Maciel 02-07-01. Brief Hardware Status. receivers. FIC. Simple hardware and firmware corrections implemented Just arrived from Saclay, under tests now at L2 test stand. CIC. One passes tests, one borderline (w/ cable length) New battery of BIST tests (F.Ends) thru Sunday.

Brief Hardware Status

E N D

Presentation Transcript

A. Maciel 02-07-01 Brief Hardware Status receivers FIC • Simple hardware and firmware corrections implemented • Just arrived from Saclay, under tests now at L2 test stand CIC • One passes tests, one borderline (w/ cable length) • New battery of BIST tests (F.Ends) thru Sunday utilities • Seem to pass all tests – but need solid CIC before final acceptance • Likely to give go-ahead for bare boards on Monday SFO MBT • Hardware tests successful • Firmware under development • VME driver in its early stages processors SLIC • Hardware and firmware done and tested (board ready) • Management and trig. algorithm software in progress ALPHA • Five boards alive – all functions enabled • Finally a platform for software development • Bring remaining boards to life – component scans

A. Maciel 02-07-01 TRIVIAL DATA CHAIN “phase-1” SLIC (4 chans) C I C M B T UAZ_tester (12 channels) SLIC (4 chans) Alpha SLIC (4 chans) DATA MODE; • no trigger, no SCL • UAZ_tester: • run_single_cycle • run_continuous • SLICs do Chan[i] wDSP[i] • mDSP (sort channels) out • MBT 3 mbt channels into alpha • Alpha pass-thru, write to file (VME) • Data carries origin signature and Byte ordering • Succession of “shorts” • Hi Byte is Channel # • Lo Byte is counter 0...7 • One muon-object length (2 ints) per channel • Each slic outputs four “objects” • Full header-trailer treatment everywhere • At least the most basic monitoring of board fns. • Check data integrity, ordering, endianess... • Run continuous w/ error counter

A. Maciel 02-07-01 “phase-1” (cont.) • NEEDS; • All drivers in place • SLIC & Alpha on a pass-thru algorithm • DSP I/O & memory management in place • Alpha write-to-file (then error counter) • WHERE; • Test Stand, two separate crates • [ uaz+cic+slic] --- [mbt + alpha] • Then single crate, TCC style • Ready to move to MCH crate sep. drivers two alphas alpha driven • WHEN; ?? [1st crate] needs are; • uaz Xmit data (1 week) , CIC is ready • SLIC • DSP (I/O & memory) management • wDSP pass-thru, and DSP_5 full algo. • Download & Boot procedures • [1st crate]-only tests possible Done in ~ 6 weeks • MEANWHILE; • mbt + alpha can get indept.data (chan-16) • normal work towards L2 commissioning • is prioritized to enable a “minimal phase-2” • (no interference w/ overall L2 build) End of “Phase-1” ; except for SCL-related issues, ~all hardware and VME-driver problems solved

A. Maciel 02-07-01 REAL DATA CHAIN “phase-2” • Inclusion of the trigger (SCL – TFW) • Inclusion of the “downstream alpha” • Otherwise, mostly a software issue • Cable up the coaxials (PP to CIC) -- CIC crate optional • Enable (n<=12) Front End crates (limited by # CICs) • Adapt DSP phys-algorithm acc. to active crates – ideallly • a subset of a definitive algorithm (e.g. scints-only) • Enable the SCL on the MBT, SLICs and Alphas ( 1 SFO ) • Event alignment + Ability to respond to SCL-Initialize. • Alpha “mucworker” and/or “mufworker” as in final version • As much monitoring data as possible (SLIC DSP5-to-VME) • How much of Global (?) – L3 (?) • Augment system as boards (or inputs) show up SLIC time estimate; ~6 weeks after completion of “phase 1”