EE19D Digital Electronics

EE19D Digital Electronics. Sequential Logic: Fundamentals and Circuits (Part two). Synchronous Sequential Networks.

EE19D Digital Electronics

E N D

Presentation Transcript

EE19D Digital Electronics Sequential Logic: Fundamentals and Circuits (Part two)

Synchronous Sequential Networks • The block diagram of figure 4 can be modified to represent a synchronous network by replacing all the memory elements by Flip-flops which are controlled by the same clock signal (figure 6). Figure 6: Synchronous sequential network

All flip-lop changes are assumed to be synchronized by a single clocking signal and change their state following the same edge of the clock. Activity in the network is cyclic with the clock signal. That activity consists of the following. • 1.Following the synchronizing clock edge: • (a)primary input variables W1, W2…….Wn may change value, • (b)flip-flop output variables y1, y2, ……yn may change value.

But all the changes must take place within a finite, know interval Tf, usually Tf is the maximum of the flip-flop propagation delays. • 2. Then the new input symbol to the combinational logic, the (n +p)-tuple (W1, W2….Wn, y1, y2…..yp), propagates through that logic to form the m output Z1, Z2, …..Zm and the flip-flop input signals. All these changes must take place within a finite interval, known as interval Tg. Tg is the maximum propagation delay through the combinational logic block.

3.Then all the flip-flop input signals must be held at their final values for an interval equal to or greater than the setup time Tsu for the flip-flops. Only after this interval it is safe to another synchronizing edge to occur. The clock period T must therefore satisfy T > Tf + Tg + Tsu for reliable behaviour in the network.

State Model Figure 7: State Model

A synchronous sequential network can be represented in two different ways (Moore and Mealy)

State-machine structure (Mealy) output depends onstate and input typically edge-triggered D flip-flops

State-machine structure (Moore) output dependson state only typically edge-triggered D flip-flops

State-machine structure (pipelined) • Often used in PLD-based state machines. • Outputs taken directly from flip-flops, valid sooner after clock edge. • But the “output logic” must determine output value one clock tick sooner (“pipelined”).

State Diagram • A state diagram is a directed graph used to represent the transition and output function in a sequential system. Each state is represented by a node and each transition by an arc. • An arc from node Sk to node Sj and labelled x/z specifies that, for a present state Sk and an input x, the next state is Sj and the output is z (figure 9).

x/z Sj Sk State Figure 9: State Diagram (Mealy) x Sj/zj Sk/zk State Figure 10: State diagram (equivalent Moore)

A finite state machine can be represented using a state diagram or a state table. Figure 11 shows different modes of representation of a Mealy Machine 1/1 0/1 S0 S1 S2 0/0p 1/0 0/0 1/1 a) State diagram

Current State S(t) Input x(t) 0 1 S0 S1,1 S2,1 S1 S1,0 S0,1 S2 S1,0 S2,1 S(t+1),z(t) b) State stable

Present Sate A B Input x Next State NA NB Output z 0 0: S0 0 0 1: S1 1 0 0: S0 1 1 0: S2 1 0 1: S1 0 0 1: S1 0 0 1: S1 1 0 0: S0 1 1 0: S2 0 0 1: S1 0 1 0: S2 1 1 0: S2 1 b) State transition table Figure 12: Different modes of representations of a finite state machine

State-machine analysis steps • Assumption: Starting point is a logic diagram. 1. Determine next-state function F and output function G. 2a. Construct state table • For each state/input combination, determine the excitation value. • Using the characteristic equation, determine the corresponding next-state values (trivial with D f-f’s). 2b. Construct output table • For each state/input combination, determine the output value. (Can be combined with state table.) 3. (Optional) Draw state diagram

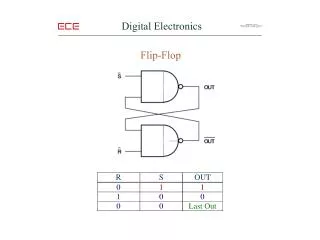

Transition equations • Excitation equations • Characteristic equations • Substitute excitation equations into characteristic equations

Transition and state tables (output equation) state/outputtable state table transitiontable another name for this function? (transitionequations)

State diagram • Circles for states • Arrows for transitions (note output info)

Modified state machine • Moore machine MAXS MAXS = Q0 Q1

Timing diagram for state machine • Not a complete description of machine behavior

c)Specification of different types of sequential systems. We will present two examples of specification of sequential systems. Additional systems are described in subsequent chapters. Modulo-p Counter: A modulo-p counter is a sequential system whose input is a binary variable and whose output has integer values from the set {0,1, 2, ……,p-1}. Its time behaviour is described as follows:

A state description requires p states. Assigning the integers 0 to p-1 as the state labels, the following description is obtained: Input: x(t) {0,1} Output: z(t) {0,1, 2,……,p-1} State: s(t) {0,1, 2,……,p-1} Initial state: s(0) = 0 Function: the transition and output functions are: s(t+1) = [s(t) + x(t)] mod p and z(t) = s(t) Figure 13 shows the state diagram of a modulo-5 counter.

Figure 13. State diagram of a modulo-5 counter. Pattern Recognizer: A pattern recognizer is a sequential system whose binary output at time t indicates whether the input subsequence ending at time t corresponds to the particular pattern recognized by the system. Consequently, a pattern recognizer is a finite memory system – A sequential system has finite memory of length m if its output z(t) depends only on the last input values, that is z(t) = F(x(t-m+1,t)).

A sequential system that recognizes the pattern P = (p0,p1,….,pm-1) has the following description: Input: x(t) I Output: z(t) {0,1} Function :

Algorithmic State Machine (ASM) • Why State diagrams are not Enough ? • Not flexible enough for describing very complex finite state machines • Not suitable for gradual refinement of finite state machine • Do not obviously describe an algorithm: that is, well specifiedsequence of actions based on input data: • algorithm = sequencing + data manipulation • separation of control and data • Gradual shift towards program-like representation: • Algorithm State Machine (ASM) Notation • Hardware Description Languages (e.g., ABEL, VHDL or Verilog)

FSMs and ASMs Example: Odd Parity Checker Assert output whenever input bit stream has odd # of 1's Symbolic State Transition Table State Diagram Encoded State Transition Table

Example: Odd Parity Checker Next State/Output Functions NS = PS xor PI; OUT = PS T FF Implementation D FF Implementation Timing Behavior: Input 1 0 0 1 1 0 1 0 1 1 1 0

FSMs/ASMs (Moore and Mealy) of the odd Parity Detector FSM Diagrams S0 00 S0 0 IN IN S1 01 S1 1 IN IN S2 10 H.OUT H.OUT ASM Diagrams IN

Concept of the Synchronous Sequential Circuit Timing: When are inputs sampled, next state computed, outputs asserted? State Time: Time between clocking events • Clocking event causes state/outputs to transition, based on inputs • For set-up/hold time considerations: Inputs should be stable before clocking event • After propagation delay, Next State entered, Outputs are stable NOTE: Asynchronous signals take effect immediately Synchronous signals take effect at the next clocking event E.g., tri-state enable: effective immediately sync. counter clear: effective at next clock event

On rising edge, inputs sampled; outputs, next state computed • After propagation delay, outputs and next state are stable • Immediate Outputs: • affect datapath immediately • could cause inputs from datapath to change • Delayed Outputs: • take effect on next clock edge • propagation delays must exceed hold times Example: Positive Edge Triggered Synchronous System

N Coin Vending Gum Open D Sensor Machine Release SSC Mechanism Reset Clk Example: Vending Machine SSC General Machine Concept: deliver package of gum after 15 cents deposited single coin slot for dimes, nickels no change Step 1. Understand the problem: Draw a picture! Block Diagram

Vending Machine Example Step 2. Map into more suitable abstract representation Tabulate typical input sequences: three nickels nickel, dime dime, nickel two dimes two nickels, dime Draw state diagram: Inputs: N, D, reset Output: open

Step 3: State Minimization reuse states whenever possible Symbolic State Table

Present State Inputs Next State Output Q Q D N D D Open 1 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 0 1 1 X X X 0 1 0 0 0 1 0 0 1 1 0 0 1 0 1 1 0 1 1 X X X 1 0 0 0 1 0 0 0 1 1 1 0 1 0 1 1 0 1 1 X X X 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 X X X Step 4: State Encoding

Parity Checker Example Q1 Q1 Q1 Q1 Q0 Q1 Q0 Q1 Q0 D N 00 01 11 10 D N 00 01 11 10 D N 00 01 11 10 0 0 1 1 0 1 1 0 0 0 1 0 00 00 00 0 1 1 1 1 0 1 1 0 0 1 0 01 01 01 N N N X X X X X X X X X X X X 11 11 11 D D D 1 1 1 1 0 1 1 1 0 0 1 0 10 10 10 Q0 Q0 Q0 Step 5. Choose FFs for implementation D FF easiest to use D1 = Q1 + D + Q0 N D0 = N Q0 + Q0 N + Q1 N + Q1 D OPEN = Q1 Q0 8 Gates

Parity Checker Example Step 5. Choosing FF for Implementation J-K FF Remapped encoded state transition table

Moore and Mealy Machines State Diagram Equivalents Moore Machine Mealy Machine Outputs are associated with State Outputs are associated with Transitions

Another design example (from text: pp. 564 - 576) • Design a machine with inputs A and B and output Z that is 1 if: • A had the same value at the two previous ticks • B has been 1 since the last time the above was true

State assignment • There are 6,720 different state assignments of 5 states to 3 variables. • And there are even more using 4 or more variables • Here are a few “obvious” or “interesting” ones: