ATLAS 実験ミューオントリガーエレクトロニクスの開発と概要

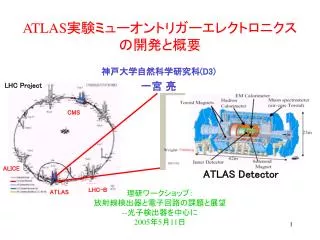

ATLAS 実験ミューオントリガーエレクトロニクスの開発と概要. LHC Project. CMS. 神戸大学自然科学研究科 (D3) 一宮 亮. ALICE. ATLAS Detector. LHC-B. ATLAS. 理研ワークショップ: 放射線検出器と電子回路の課題と展望 -- 光子検出器を中心に 2005 年 5 月 11 日. Physics potential at LHC. Higgs, SUSY 発見を始めとする、 ~1TeV までのエネルギーフロンティアの新物理を開拓する実験。 t, b や W/Z 粒子の精密測定実験。 ( 膨大な生成量 ).

ATLAS 実験ミューオントリガーエレクトロニクスの開発と概要

E N D

Presentation Transcript

ATLAS実験ミューオントリガーエレクトロニクスの開発と概要ATLAS実験ミューオントリガーエレクトロニクスの開発と概要 LHC Project CMS 神戸大学自然科学研究科(D3) 一宮 亮 ALICE ATLAS Detector LHC-B ATLAS 理研ワークショップ: 放射線検出器と電子回路の課題と展望 --光子検出器を中心に 2005年5月11日

Physics potential at LHC • Higgs, SUSY発見を始めとする、~1TeVまでのエネルギーフロンティアの新物理を開拓する実験。 • t, bやW/Z粒子の精密測定実験。(膨大な生成量) Event rate at low luminosity (1033/cm2/s) Higgs discovery sensitivity 5 sigma 100 GeV 1 TeV

ATLAS Detector • 陽子コライダー • 重心エネルギー: 14TeV • Luminosity: 1034/cm2/s (at high lumi.) • 高いバンチ衝突頻度 • 40MHz (25ns) • ~20 Interactions/bunch(min. bias) ⇒確実なバンチ識別が可能な、高速な トリガ用検出器と専用エレクトロニクスが必要 (Level-1 Trigger:40MHz ⇒75kHz) H → γγ • Inner Tracker • Calorimeter(EM, Hadron) • Muon Spectrometer • トリガ用測定器 • Thin Gap Chamber(TGC) [エンドキャップ部] • Resistive Plate Chamber(RPC) [バレル部] • 精密測定器 • Monitored Drift Tube(MDT) ATLAS Detector Event Display without pile-up (at high lumi.) Event Display with pile-up (at high lumi.)

ATLAS Trigger System • 3段階の Trigger Selection • *Triggerされた データは読み出される • (Trigger) (Readout) ATLAS Trigger System • Level-1 Trigger • バンチ交差周波数(40MHz)に同期したPipeline処理。 • トリガ用検出器(Muon, Calo.)からの信号を用いて、トリガレートを75kHzまで絞る。(max:100kHz) • Bunch ID の付加。 • 許容Latency:2μs • 採択されたデータは全検出器のPipeline Memory から読み出される。Readout • Level-2 Trigger • Level-1 Trigger で選択されたRoIから読み出す。(RoI Mechanism) • Event Filter • Computer Farm での処理。 75kHz→

Pick-up strip FR4 layer Graphite layer Thin Gap Chamber(TGC) Pick-up stripによって 二次元読出しが可能 構造図(T7 type) 断面図 17 ~41 1365 動作条件 • wire potential ~3.1kV • gas mixture CO2-n-pentane(55:45) • gas amplification 10^6 要求される仕様: • time jitter ≦25ns • efficiency > 99% • rate capability > 100Hz/cm^2 • long term stability ~ 10 years 1245 単位:mm 1200 等電位面 9 ~ 57 2種類のスペーサー ワイヤーグルーピング

TGC Trigger System R 方法: ミューオンのトラックfinding + 磁場による横運動量(pT)解析 3プレーンのチェンバ配置(M1, M2, M3) On-Detector Electronics 無限運動量トラック (衝突点とM3間の直線) からのずれを数値化 • 合計 ~320,000 channels の入力 • この多チャンネルを効率よく処理するために、出来る限り多くのエレクトロニクスは、On-Detector(実験室内) に設置したい。(channel 単価を安くすべし!) • 実験室外への信号は全て光ファイバーによるシリアルリンク(~100m)で行う。 • Low-pT 判定 • M2でのずれを測定(R, φ) • High-pT判定 • M1でのずれを測定(R, φ) • R-φ統合

TGC Electronics 3つの主要パス (1)Trigger Level-1 判定のためのトリガ候補の 選出 (40MHzでのpipeline 動作) (2)Readout Level-1 判定されたイベントの データを読み出し (最大75kHz) (3)Control パラメータの設定などモジュールの 制御 (slow control) PS Board * * ASD *初段の、ASD(Amp.-Shaper-Discri.), PP(Patch Panel; タイミング調整回路)以外は全てロジック(デジタル)回路。 実験ホール (放射線環境) エレキ ハット 光リンク(100m) SL ROD PS Board HPT SSW HSC CCI

TGCエレクトロニクスとその放射線環境 • TGC エレクトロニクスで使用する電子回路素子では、10年で • 23.8krad (電離放射線による吸収線量) • 5.6x1011 hadrons/cm2 の放射線に耐えなければならない。 (Safety Factor含む) エレキハット 実験ホール この環境下で、懸念される影響 ↓ • Single Event Effect (SEE)[確率的現象]による影響 ← 5.6x1011 hadrons/cm2 • メモリ及びレジスタ値の反転。(TGCエレクトロニクスの環境では、数分に1回程度) • FPGA/CPLDのconfiguration data(デバイス内部のSRAMに記録)が変化し、異なった回路に変化してしまう。 • Total Ionizing Doze(TID)[蓄積効果]による影響 ← 23.8krad • 特性の変化(動作速度の低下、消費電流の増加)。 • 最悪の場合、デバイスが永久故障する。(基板の交換は困難) • CPLDなど不揮発性の Flash/EPROM構造をもつデバイスは、内部昇圧回路の放射線損傷により再書き込みが出来なくなる可能性がある。 • =>FPGA/CPLDは、使用困難!

多数決論理回路 (Voting Logic, TMR) Anti-Fuse FPGA • Anti-Fuse FPGA(Actel, QuickLogic) • 回路構成は、 configuration memory ではなく、Open 状態のAnti-Fuseを Shortさせることにより決定される(焼き切り型で、再プログラム不可)。 • コンタクト抵抗が少ないため、FPGAの中では最も高速。 • 宇宙・航空用途に多く採用実績があり、ASICと同様にSEUによるレジスタ値の書き換わりを訂正する多数決ロジック(Voting Logic, TMR)のライブラリが用意されている。 Anti-Fuse

ASIC FPGA(Anti-fuse) デバイスの選択 PS-Pack HSC Crate エレキハット 実験ホール

Input JTAG Readout Trigger ASICDevelopment (SLB ASIC) • 4ブロックで構成 • Input (mask, delay調整) • JTAG(レジスタ設定用) • Trigger(Low-pT判定; 40MHz動作) • Readout(読み出し系; 75kHz読み出し) • ROHM 社 0.35mm CMOS • セルベースASIC (3metal+1poly) • ダイサイズ: 9.86mm x 9.86mm • I/O ピン数: 256 (QFP) • 800Kゲート相当 • ランダムロジック: 200Kゲート • メモリ: 600Kゲート (56kbit) • 160bit入力、(40+5)bit出力。

SLB ASIC開発で遭遇した問題点 • 放射線環境下で用いられるため、対策(レジスタは多数決回路で構成)が必要。 • 「配線遅延>ゲート遅延」のため、Flip-Flopでタイミング違反(Setup/Hold)が発生しやすい。 • データが化ける原因。 • 論理合成の問題。 • 過多fanout信号の生成。 • Etc...

「配線遅延>ゲート遅延」の問題 • プロセスが微細化すると、配線遅延が無視出来なくなってくる。 • 特に、単純なシフトレジスタの場合、以下の様な現象が起こり得る。 解決策:負エッジD-Flip Flop と正エッジD-Flip Flopの組み合わせによるMaster-Slave方式の採用。 clock clock 配線遅延 配線遅延 data clock data clock setup hold setup hold

対策 • Design Compilerのバージョンを 2001.08以降にして、適切なオプション設定にした所、この現象は発生しなくなった。 ~440 fanouts (PSC@Readout Block) 論理合成の問題 • 古いDesign Compiler (2000.05)の奇妙な振る舞い。 • 各module 内の全ての負エッジD-Flip Flop の clock 入力が、clock ラインにインバータ2個を挿入した出力に接続されてしまう。 • 通常は、Flip Flop のクロック入力には、何もゲートが接続されず、Clock Tree が負荷分散しながら、等長配線してくれる。 • 結果 • ある試作では、30MHzまでしか動作しなかった。 clock tree末端

Summary TGCエレクトロニクスシステム 放射線環境下で、~320,000chに及ぶ入力信号を効率よく処理するため、可能な限り多くのエレクトロニクスを、On-Detector(実験室内) に設置した。 初段のトリガシステムであるため、低latencyが要求され(<2ms)、全てハードウェアロジックで実装している。 On-detectorに設置されるエレクトロニクスのデバイスは、全て耐放射線のチェックを行った。その結果、FPGA/CPLDは回路が書き換わるため、使用出来ないことが判明した。 ASIC Development ASIC の製作では、多数決論理による放射線対策の他に、 Master-Slave 方式の採用や、クロックツリーの構築など、ASIC特有の手法を施す必要があった。 また、千個以下しか使用数がなく、アナログ回路を含まない場合には、Anti-Fuse型FPGAを利用するのが良い。

CMOS ASIC(Rohm 0.35 um) • γ線照射結果 (TID, 蓄積ダメージ) • 50kradまでは、顕著な消費電流の増加はない。 • VCO(PLLの制御電圧; 低いほどトランジスタの動作速度が速い)も、30kradではほとんど変化がない。 • 照射後の動作確認の結果、全サンプルとも正常に動作した。 23krad 23krad VCO Voltage(V) 0 20 40 60 80 100 Absorbed Dose(krad) 0 20 40 60 80 100 Absorbed Dose(krad)