VLSI Physical Design: RW Clustering and Label Computation

80 likes | 138 Views

Perform RW clustering on a di-graph with inter-cluster delay, node delay, and size limit. Compute labels and clusters for practical problems in VLSI physical design. Generate labeling and clustering information.

VLSI Physical Design: RW Clustering and Label Computation

E N D

Presentation Transcript

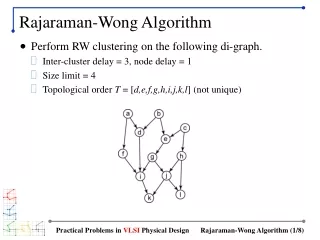

Rajaraman-Wong Algorithm • Perform RW clustering on the following di-graph. • Inter-cluster delay = 3, node delay = 1 • Size limit = 4 • Topological order T = [d,e,f,g,h,i,j,k,l] (not unique) Practical Problems in VLSI Physical Design

Max Delay Matrix • All-pair delay matrix Δ(x,y) • Max delay from output of the PIs to output of destination Practical Problems in VLSI Physical Design

Label and Clustering Computation • Compute l(d) and cluster(d) Practical Problems in VLSI Physical Design

Label Computation • Compute l(i) and cluster(i) Practical Problems in VLSI Physical Design

Labeling Summary • Labeling phase generates the following information. • Max label = max delay= 8 Practical Problems in VLSI Physical Design

Clustering Phase • Initially L = POs = {k,l}. Practical Problems in VLSI Physical Design

Clustering Summary • Clustering phase generates 8 clusters. • 8 nodes are duplicated Practical Problems in VLSI Physical Design

Final Clustering Result • Path c-e-g-i-k has delay 8 (= max label) Practical Problems in VLSI Physical Design