VHDL Description-2

E N D

Presentation Transcript

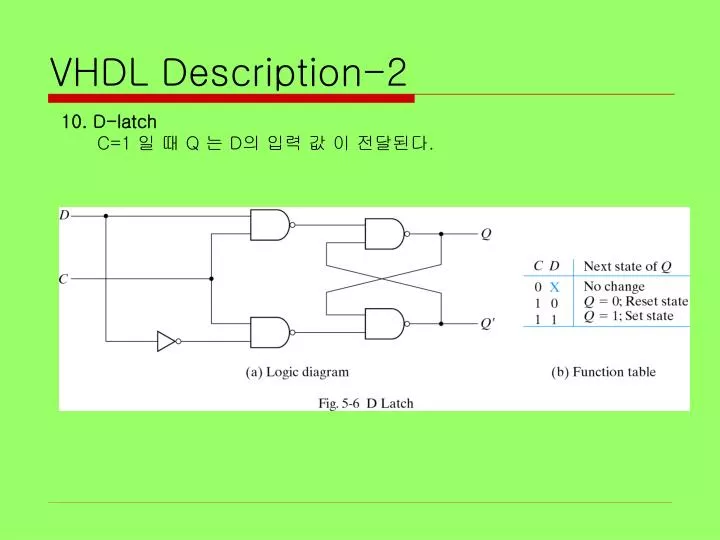

VHDL Description-2 10. D-latch C=1 일 때 Q 는 D의 입력 값 이 전달된다.

VHDL Description-2 10. D-latch library ieee ; use ieee.std_logic_1164.all; entity D_latch is port( D_in : in std_logic; C_en : in std_logic; Q_out: out std_logic ); end D_latch; architecture behv of D_latch is begin process(D_in, C_en) begin if (C_en='1') then -- no clock signal here Q_out <= D_in ; end if; end process; end behv;

VHDL Description-2 11. D-FF D-latch 는 CLK 가 없고 C : enable 로 동작, D-FF 은 CLK 에 의해 동작 상승 엣지에서 Q+=D 동작 하강 엣지에서 Q+=D 동작

VHDL Description-2 11. 상승 엣지 동작 D-FF library ieee ; use ieee.std_logic_1164.all; use work.all; entity dff is port( D_in: in std_logic; clock: in std_logic; Q_out: out std_logic ); end dff; architecture behv of dff is begin process(D_in, clock) begin -- clock rising edge if (clock='1' and clock'event) then Q_out <= D_in ; end if; end process; end behv;

VHDL Description-2 12. J-K FF : Set(J), Reset(K), Complement(J=K=1) 의 3동작을 구현 Q+=JQ′+K′Q

VHDL Description-2 12. 상승 엣지 JK-FF library ieee; use ieee.std_logic_1164.all; entity JK_FF is port ( clock: in std_logic; J, K: in std_logic; reset: in std_logic; Q, Qbar: out std_logic ); end JK_FF; architecture behv of JK_FF is signal state: std_logic; signal input: std_logic_vector(1 downto 0); begin -- combine inputs into vector input <= J & K; p: process(clock, reset) is begin if (reset='1') then state <= '0'; elsif (clock='1' and clock'event) then case (input) is when "11" => state <= not state; when "10" => state <= '1'; when "01" => state <= '0'; when others => state <= null ; end case; end if; end process; Q <= state; Qbar <= not state; end behv;

VHDL Description-2 13. 8 to 3 encoder : 2ⁿ 개의 입력값에 대해 n개의 출력을 생성 우선순위 인코더 : 동시에 둘 이상의 입력값이 1인 경우 문제 발생 회로에 우선 순위를 부여하여 해결한다.

VHDL Description-2 13. 우선 순위 8 to 3 encoder LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY enc8to3 IS PORT(SIGNAL input: IN std_logic_vector(7 DOWNTO 0) ; SIGNAL output: OUT std_logic_vector(2 DOWNTO 0)) ; END enc8to3 ; ARCHITECTURE arch1 OF enc8to3 IS BEGIN output <= "111" WHEN (input(7) = '1') ELSE "110" WHEN (input(6) = '1') ELSE "101" WHEN (input(5) = '1') ELSE "100" WHEN (input(4) = '1') ELSE "011" WHEN (input(3) = '1') ELSE "010" WHEN (input(2) = '1') ELSE "001" WHEN (input(1) = '1') ELSE "000" ; END arch1 ;

VHDL Description-2 14. Register : 2진 정보의 저장 • Clock=1 ;입력 정보 로딩 • Clock=0 ;레지스터 변화 없음. • Load input=1 ; 레지스터에 입력 I 전송 • Load input=0 ; 레지스터에 정보 저장. • Clear 가 D-FF 에 연결된 경우 Clear=1 ; 출력을 모두 0로 만듬

VHDL Description-2 14. n-bit Register library ieee ; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity reg is generic(n: natural :=2); port( I: in std_logic_vector(n-1 downto 0); clock: in std_logic; load: in std_logic; clear: in std_logic; A: out std_logic_vector(n-1 downto 0)); end reg; architecture behv of reg is signal Q_tmp: std_logic_vector(n-1 downto 0); begin process(I, clock, load, clear) begin if clear = '0' then Q_tmp <= Q_tmp-Q_tmp; elsif (clock='1' and clock'event) then if load = '1' then Q_tmp <= I; end if; end if; end process; A <= Q_tmp; end behv;

VHDL Description-2 15. Asynchronous reset 16-counter : 0-15 까지 카운트하는 카운터 (reset 신호가 1일때 출력은 “0000” library ieee ; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity count_16 is port( clk,reset : in std_logic; q: out std_logic_vector(3 down to 0) ); End count_16 Architecture beha of count_16 is Begin process (clk, reset) variable temp : std_logic_vector(3 downto 0):=‘’0000’’ begin if reset=‘0’ then temp:=“0000”; elsif (clk’event and clk=‘1’) then if temp=15 then temp:=“0000”; else temp:=temp+1; end if; end if: q <= temp; End process; End beha;

VHDL Description-2 16. Up-down Counter : clk 및 updn 신호 에 의해 카운트를 증가 (상향식) 및 카운트를 감소 (하향식) 시키는 카운터 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity UpDncnt4 is port( clk,nclr : in std_logic; -- clk is clock, nclr is clear UpDn : in std_logic; -- updn =1 (up counter), updn= 0 (down counter) q3,q2,q1,q0 : out std_logic); end UpDncnt4; architecture a of UpDncnt4 is signal q : std_logic_vector( 3 downto 0); begin process(nclr,clk) begin if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then if( UpDn='1') then q <= q+'1'; else q <= q-'1'; end if; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); end a;