Cache Interference I

Explore the impact of cache interference on SMT and conventional multi-threaded architectures, including positive and negative interference effects. Learn about solutions like separate data and instruction caches and dynamic cache structures. Referencing key studies on maximizing on-chip parallelism through simultaneous multithreading.

Cache Interference I

E N D

Presentation Transcript

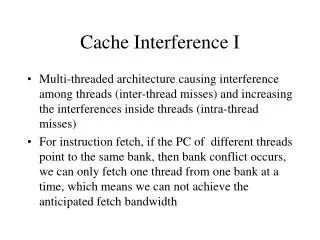

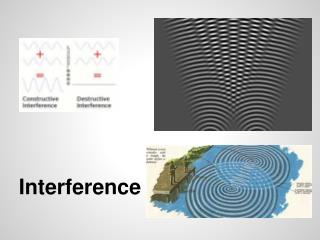

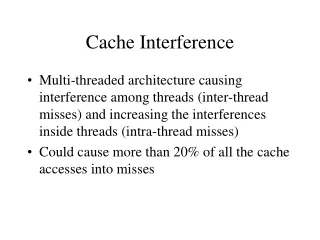

Cache Interference I • Multi-threaded architecture causing interference among threads (inter-thread misses) and increasing the interferences inside threads (intra-thread misses) • For instruction fetch, if the PC of different threads point to the same bank, then bank conflict occurs, we can only fetch one thread from one bank at a time, which means we can not achieve the anticipated fetch bandwidth

Cache Interference II • It’s not only a problem for SMT [3], it comes to people’s attention also in conventional multithreaded architecture (context switch) [1], which shows similar results. • Conventional caches are not suitable for the multi-threading architecture

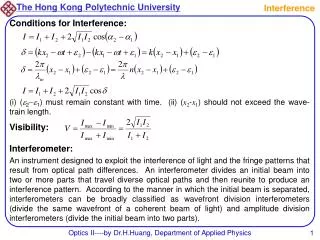

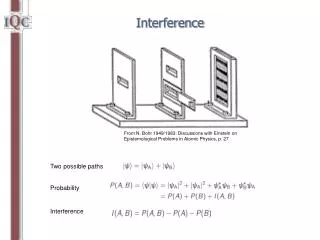

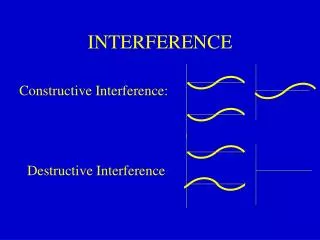

Cache interference can be positive and negative • Positive interference happens when one context serves to load the cache with code or data that is also needed by another context. It is performing a limited pre-fetch for the other context, and cache miss rates are lowered • The information cached by one context can knock out data needed by another context, this is negative interference and leads to a higher miss rate • But the negative interference dominates over positive interference

Cache structure • For SMT, Shared Data Cache and Private Instruction Cache provide the best performance [2] • Normally we have separate L-1 D-Cache and I-Cache

Propose • then for I-cache, I prefer splitted cache [4]. Split the cache into equal sized part, each one is assigned to a running thread, then we solve the problem of bank conflict for instruction fetch • While for the D-cache, I prefer some dynamic structure cache

Reference • Wolf-Dietrich Weber and Anoop Gupta, “Exploring the benefits of multiple hardware contexts in a multiprocessor architecture: Preliminary Results”, ISCA’89 • D.M. Tullsen, S.J. Eggers, and H.M. Levy, “Simultaneous Multithreading: Maximizing On-Chip Parallelism”, ISCA’95 • Jack L. Lo, Susan J. Eggers, Joel S. Emer, Henry M. Levy, Rebecca L. Stamm, and Dean M. Tullsen, “Converting Thread-Level Parallelism Into Instruction-Level Parallelism via Simultaneous Multithreading”, ACM Transactions on Computer Systems, August 1997 • Montse Garcia, Jose Gonzalez and Antonio Gonzalez, “Data Caches for Multithreaded Processors”, in Multi-Threaded Execution, Architecture and Compilation Workshop (MTEAC), January 2000