Functional Verification in Teaching: Enhancing Computer Engineering Education

Join this workshop on teaching functional verification to expand curriculums, collaborate, and utilize automated testbench concepts. Discover the importance of verification in the chip industry and learn about course evolution and industry partnerships.

Functional Verification in Teaching: Enhancing Computer Engineering Education

E N D

Presentation Transcript

Teaching Functional Verification Design Automation Conference Sunday, June 9, 2002

Workshop Goals • Share experiences in teaching functional verification • Initiate collaborative efforts to extend the teaching of functional verification • Expand Computer Engineering curriculums to include functional verification

Agenda • Workshop Overview • Textbook Overviews • Course Organization and Management • Lab Exercise Overview • Automated Testbench Concepts • Formal Verification and Rulebase

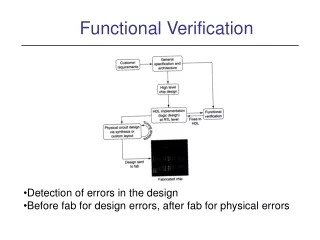

Why is verification so important to the chip industry? • Verification is the single biggest lever to effect the triple constraints: Schedule, Cost, & Quality • Fewer revs through the fabrication process means lower costs and faster time-to-market • Re-spinning a chip costs: • Hundreds of thousands of dollars • 6-8 weeks • So if you can get it right in fewer "passes", you WIN!!!

What Industry Has Found • The system and chip industry depends on functional verification • There’s a science and methodology behind verification • Verification has a separate career path from logic and circuit design

Course Evolution • IBM internal class • Initial 2 day class with 1 lab • Current 2 week (80 hour) format • University Partnerships followed initial course

University Participation • Penn State, Pittsburgh and North Carolina State have completed full semester courses on functional verification • Active class at Ohio State (quarters) • There’s now a foundation of resources for other university professors to build upon

Notes: • Web address: http://www.cse.psu.edu/~vijay/verify/instructors.html Open to university professors doing verification classwork. Industry access granted for adding to body of knowledge. • Tool/Vendor specifics • Universities should take advantage of any current vendor agreements they have • Materials are “vendor agnostic” • Simulation engines, Specman, VERA • Recognition for all slides must be maintained

Contacts • Vijay Narayanan, PSU (vijay@cse.psu.edu) (Web page owner) • Steve Levitan, Pitt (steve@ee.pitt.edu) • John Goss, NCSU (gossman@us.ibm.com) • Bruce Wile, IBM (bwile@us.ibm.com) • Matthew Morley, Verisity’s University partnerships (matthew@verisity.com • Yaron Wolfsthal, IBM’s Rulebase (wolfstal@il.ibm.com) • Janick Bergeron, Qualis Corp, “Writing Testbenches” textbook, & Verification Guild Newsletter (janick@bergeron.com) • Faisal Haque, Cisco, “Art of Verification” textbook (fhaque@cisco.com)