第 5 章 时序逻辑电路

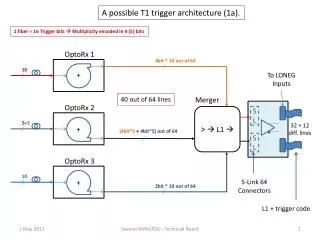

第 5 章 时序逻辑电路. 5.1 概述 5.2 时序逻辑电路的分析 5.3 寄存器 5.4 计数器 5.5 时序逻辑电路的设计. 5.1 概述. x. z. 1. 1. …. …. x. z. n. m. 组合逻辑电路. …. …. q. y. 1. 1. q. y. 存储电路. j. k. 一、时序逻辑电路的组成. 时序逻辑电路:任一时刻的输出信号不仅取决于该时刻的输入信号,而且还取决于电路原来的状态。它由组合逻辑电路和存储电路组成。. 逻辑关系:. 输出方程. 驱动方程. 状态方程.

第 5 章 时序逻辑电路

E N D

Presentation Transcript

第5章 时序逻辑电路 5.1 概述 5.2 时序逻辑电路的分析 5.3 寄存器 5.4 计数器 5.5 时序逻辑电路的设计

5.1 概述 x z 1 1 … … x z n m 组合逻辑电路 … … q y 1 1 q y 存储电路 j k 一、时序逻辑电路的组成 时序逻辑电路:任一时刻的输出信号不仅取决于该时刻的输入信号,而且还取决于电路原来的状态。它由组合逻辑电路和存储电路组成。 逻辑关系: 输出方程 驱动方程 状态方程 向量函数形式:

5.1 概述 & Z & & Z Q Q 0 1 Q 1 J 1 J 1 J 2 Q Q Q CP 0 1 2 1 J 1 J 1 J C 1 C 1 C 1 C 1 C 1 C 1 1 K 1 K 1 K 1 K 1 K 1 K FF FF FF 0 1 2 FF FF FF CP 0 1 2 二、时序逻辑电路的分类 同步时序逻辑电路 按照触发器的动作特点 所有触发器的状态变化都是在同一时钟信号作用下同时发生的。 异步时序逻辑电路 没有统一的时钟脉冲信号,各触发器状态的变化不是同时发生,而是有先有后。 米里(Mealy)型 按照输出信号的特点 输出状态不仅与存储电路的状态Q有关,而且与外部输入X也有关。 摩尔(Moore)型 输出状态仅与存储电路的状态Q有关,而与输入X无直接关系。或者没有单独的输出。

5.1 概述 三、时序逻辑功能的描述方法 1.逻辑方程式 输出方程 驱动方程(激励方程、输入方程) 状态方程 2.状态转移表 时序逻辑电路状态表 状态转移表也称状态迁移表或状态表,是用列表的方式来描述时序逻辑电路输出Z、次态Qn+1和外部输入X、现态Qn之间的逻辑关系。

5.1 概述 000 001 010 011 X X Z / 1 0 01/1 01/1 111 110 101 100 Q Q 1 0 11/0 11/0 00 01 Q Q Q 2 1 0 11/0 10/1 10/1 11/0 01/1 10 11 10/1 10/1 3.状态转移图 状态转移图也称状态图,是用几何图形的方式来描述时序逻辑电路输入X、输出Z以及状态转移规律之间的逻辑关系。 4.时序图(波形图) 时序图即为时序电路的工作波形图,它以波形的形式描述时序电路内部状态Q、外部输出Z随输入信号X变化的规律。

5.2 时序逻辑电路的分析 时序逻辑电路的分析,就是根据给定的时序逻辑电路图,找出该时序逻辑电路在输入信号及时钟信号作用下,电路的状态及输出的变化规律,从而了解该时序逻辑电路的逻辑功能。 一、时序逻辑电路的分析方法 ① 根据给定逻辑图,写出时序电路的输出方程和各触发器的驱动方程; ② 将驱动方程代入所用触发器的特征方程,获得时序电路的状态方程; ③ 根据时序电路的状态方程和输出方程,建立状态转移表; ④ 由状态转移表画出状态图,进而画出波形图。 ⑤ 分析电路的逻辑功能。

5.2 时序逻辑电路的分析 & Z “1” FF FF X 1 0 Q Q = 1 1 0 1 J 1 J C 1 C 1 Q Q 1 0 1 K 1 K CP 二、同步时序逻辑电路的分析举例 例:分析下图所示同步时序电路的逻辑功能。 解:① 求驱动方程和输出方程 (米里型)

5.2 时序逻辑电路的分析 0/0 X Z / Q Q 00 01 1 0 1/0 0/0 1/1 1/0 0/0 1/0 11 10 0/0 ② 求状态方程 ③ 列状态表 ④ 画状态图

5.2 时序逻辑电路的分析 1 2 3 4 5 6 7 8 9 CP 0/0 X Z / X Q Q 00 01 1 0 1/0 Q 1 0/0 1/1 1/0 0/0 Q 1/0 0 11 10 Z 0/0 ⑤ 画工作波形图 设Q1Q0的初始状态为00。

5.2 时序逻辑电路的分析 0/0 X Z / Q Q 00 01 1 0 1/0 0/0 1/1 1/0 0/0 1/0 11 10 0/0 ⑥ 逻辑功能分析 分析得: 当外部输入X=0时,状态转移按00→01→10→11→00→…规律变化,实现模4加法计数器的功能;当X=1时,状态转移按00→11→10→01→00→…规律变化,实现模4减法计数器的功能。所以,该电路是一个同步模4可逆计数器。X为加/减控制信号,Z为借位输出。

5.2 时序逻辑电路的分析 练习:分析下图所示同步时序电路的逻辑功能。

5.2 时序逻辑电路的分析 解:① 求输出方程和驱动方程 (摩尔型) ② 求状态方程 ③ 列状态表

5.2 时序逻辑电路的分析 1 2 3 4 5 6 CP Q 2 Q 1 Q 0 ④ 画状态图 ⑤画波形图 设Q2Q1Q0的初始状态为000。

5.2 时序逻辑电路的分析 ⑥ 逻辑功能分析 从以上分析可以看出,该电路在CP脉冲作用下,把宽度为T的脉冲以三次分配给Q0、Q1和Q2各端,因此,该电路是一个脉冲分配器。由状态图和波形图可以看出,该电路每经过三个时钟周期循环一次,并且该电路具有自启动能力。 闭合回路中的为“有效状态” 闭合回路外的为“无效状态” 当电路处于任一无效状态时,若能在时钟信号作用下进入有效状态,称该电路具有自启动能力;否则,该电路无自启动能力。

5.2 时序逻辑电路的分析 FF FF FF 0 1 2 Q Q Q & 1 0 2 1 1 J J 1 J CP2 CP0 C C 1 1 C 1 CP1 Q Q Q 1 0 2 1 1 K K 1 K CP 三、异步时序逻辑电路的分析举例 例:分析下图所示异步时序电路的逻辑功能。 解:① 求驱动方程 (摩尔型)

5.2 时序逻辑电路的分析 ② 求状态方程 ③ 列状态表 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 0 1 0 0 0 0 1 0 1 1 0 0 0 0 0 0 0 0 0 0 1 1 0

5.2 时序逻辑电路的分析 100 111 110 101 011 010 001 000 Q2Q1Q0 ④ 画状态图 ⑤ 逻辑功能分析 分析得: 该电路是一个异步五进制(模5)加法计数器电路,且电路具有自启动功能。

5.2 时序逻辑电路的分析 练习:分析下图所示异步时序电路的逻辑功能。 解:① 求驱动方程 (摩尔型) ② 求状态方程

5.2 时序逻辑电路的分析 100 111 110 101 011 010 001 000 Q2Q1Q0 ③ 列状态表 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 0 1 0 1 0 1 0 ④ 画状态图

5.2 时序逻辑电路的分析 CP Q 0 Q 1 Q 2 ⑤ 画波形图 设Q2Q1Q0的初始状态为000。 ⑥ 逻辑功能分析 由状态图可以看出,在时钟脉冲CP的作用下,电路的8个状态按递减规律循环变化,即: 000→111→110→101→100→011→010→001→000→… 电路具有递减计数功能,是一个3位二进制异步减法计数器,且具有自启动功能。

5.3 寄存器 输入输出方式 在数字电路中,用来存放一组二进制数据或代码的电路称为寄存器。 寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,存放n位二进制代码的寄存器,需用n个触发器来构成。 按照功能的不同,寄存器分为数码寄存器(基本寄存器)和移位寄存器两大类。 并行方式 每一位数据对应一个输入端(或输出端)。在时钟脉冲作用下,各位同时输入(或输出)。 串行方式 只有一个输入端(或输出端)。在时钟脉冲作用下,各数码逐位输入(或输出)。

5.3 寄存器 1 1 0 1 0 0 0 0 Q Q Q Q 3 2 1 0 R S R S R S R S ①清0 0 0 1 0 & & & & ②接收 D D D D 3 2 1 0 1 1 0 1 一、数码寄存器 在数码寄存器中,数据的输入、输出均为并行方式。 1.两步(二拍)接收4位数据寄存器 并行输出 “1” 并行输入

5.3 寄存器 Q Q Q Q 3 2 1 0 C 1 1 D C 1 1 D C 1 1 D C 1 1 D 接收 D D D D 3 2 1 0 1 1 0 1 1 1 0 1 2.一步(单拍)接收4位数据寄存器

5.3 寄存器 Q Q Q Q Q Q Q Q 2 2 3 3 1 1 0 0 FF FF FF FF 2 3 1 0 Q Q Q Q C1 C1 C1 C1 1D 1D 1D 1D R R R R ∧ ∧ ∧ ∧ CP 1 R D 1 D D D D 0 2 3 1 74LS175四位数据寄存器

5.3 寄存器 Q Q Q Q 0 1 2 3 FF FF FF FF 0 1 2 3 D I 1 D 1 D 1 D 1 D D C 1 C 1 C 1 C 1 o R R R R CP 用D触发器构成的移位寄存器 清0 二、移位寄存器 移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据可以并行输入、并行输出;串行输入、串行输出;并行输入、串行输出;串行输入、并行输出。十分灵活。 1.单向移位寄存器 并行输出 0 0 0 0 串行输入 1 1 0 1 “1011” 串行输出

5.3 寄存器 1 2 3 4 5 6 7 8 CP D 1 0 1 1 I 1 Q 0 1 Q 1 0 Q 2 1 0 1 1 Q 3 移位寄存器中数码移位情况 波形图

5.3 寄存器 并行输出 Q Q Q Q 1 2 3 0 串行输出 D I 串行输入 FF FF FF FF 1 2 3 0 D D D D 0 3 1 2 1D 1D 1D 1D Q Q Q Q ∧ ∧ ∧ ∧ C1 C1 C1 C1 R R R R CP CR 左移寄存器

5.3 寄存器 M 1 D D 1 IR IL 1 串行输入 串行输入 & & & & (右移) (左移) ≥1 ≥1 ≥1 ≥1 FF FF FF FF 2 3 0 1 1D 1D 1D 1D ∧ ∧ ∧ ∧ C1 C1 C1 C1 Q Q Q Q R R R R D CP OR RD 串行输出 D (右移) OL 串行输出 Q Q Q Q 0 3 2 1 (左移) 2.双向移位寄存器 M=1:右移 M=0:左移 移位控制 并 行 输 出

5.3 寄存器 74194---4位双向移位寄存器

5.3 寄存器 Q Q Q Q 1 3 0 2 ∧ CP S 0 74194 S 1 D IR D IL D D D R D 1 2 0 3 D 74194---4位双向移位寄存器 74194功能表

5.4 计数器 在数字电路中,能够记忆输入脉冲个数的电路称为计数器。计数器是一个周期性的时序电路,其状态图有一个闭合环,闭合环循环一次所需要的时钟脉冲的个数称为计数器的模值M。由n个触发器构成的计数器,其模值M一般应满足2n-1<M≤2n。 计数器有许多不同的类型: ①按时钟控制方式来分,有异步、同步两大类; ②按计数过程中数值的增减来分,有加法、减法、可逆计数器三类; ③按模值来分,有二进制、十进值和任意进制计数器。

5.4 计数器 一、二进制计数器 同步二进制加法计数器 分析: ①驱动方程和输出方程

5.4 计数器 ②状态方程 ③状态表 0 0 0 1 1 1 1 0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 0 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0

5.4 计数器 000 100 001 010 011 101 110 111 Z 1 2 3 4 5 6 7 8 0 0 0 0 0 0 0 1 CP Q 0 Q 1 Q 2 Q2Q1Q0 Z ④ 画状态图 ⑤ 画波形图 设初态为Q3Q2Q1Q0=0000。 fCP 1/2fCP 1/4fCP 1/8fCP

5.4 计数器 74161--4位同步二进制加法计数器

5.4 计数器 74161 功能表

5.4 计数器 二、十进制计数器 同步十进制加法计数器 分析: ①驱动方程和输出方程

5.4 计数器 ②状态方程

5.4 计数器 ③状态表 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 0 0 0 0 0 0 1 1 0 1 0 1 0 1 0 0001111000011110 0110011000100010 1010101010101010 0000000010101010

5.4 计数器 101 0 1011 111 0 1111 Q Q Q Q 3 2 1 0 000 0 000 1 001 0 0011 010 0 110 0 110 1 010 1 100 1 100 0 0111 011 0 6 7 9 10 1 2 3 4 5 8 CP Q 3 Q 2 Q 1 Q 0 具有自启动能力。 ④状态图 ⑤波形图 设初态为Q3Q2Q1Q0=0000。

5.4 计数器 Q Q Q Q 2 0 3 1 ET C 74160 EP CP ∧ L D D D R D D 2 1 3 0 D 74160--同步十进制加法计数器

5.4 计数器 S S S S 0 1 2 3 M个 S N-1 S S N-2 M-2 N-M个 S S S N-3 M M-1 三、任意进制计数器 假定已有的是N进制计数器,而需要得到M进制计数器。 1.当M<N时:应使计数过程中跳过N-M个状态,在M个状态中循环即可。 1)置零法(清零法或复位法) --适用于有清“0”输入端的集成计数器。 基本思路:计数器从全“0”状态S0开始计数,计满M个状态后产生清“0”信号,使计数器恢复到初态S0。 ①异步清零计数器: 利用SM状态进行译码产生清“0”信号。 ②同步清零计数器: 利用SM-1状态进行译码产生清“0”信号。

5.4 计数器 S S S 0 i i+1 S S N-1 i+2 N-M个 M个 S N-2 S S S S i+M-2 N-3 i+M-1 i+M 2)置数法(置位法) --适用于有预置数功能的集成计数器。 基本思路:计数器从某个预置状态Si(一般选S0)开始计数,计满M个状态后产生置数信号,使计数器恢复到预置初态Si。 ①异步置数计数器: 利用Si+M(或SM)状态进行译码产生置数信号。 ②同步置数计数器: 利用Si+M-1(或SM-1)状态进行译码产生置数信号。

5.4 计数器 S 0 预置数 S N-M-1 S N-M 预置数 S N-2 S N-1 3)利用进位输出位C置数法(置位法) --适用于有预置数功能的集成计数器。 ①异步置数计数器: 用SN-M-1作为预置数。 M个 ②同步置数计数器: 用SN-M作为预置数。 M个

5.4 计数器 1 1 & CP 1 & 1 CP 例:用74161实现十二进制计数器。 解:74161是具有异步清零和同步置数功能的加法计时器。 ①异步清“0”法 SM=S12 即Q3Q2Q1Q0=1100 ②同步置数法 预置数:D3D2D1D0=0000 SM-1=S11 即Q3Q2Q1Q0=1011

5.4 计数器 Q3Q2Q1Q0 1 1000 1101 1100 1011 1001 1010 0111 0101 0100 0011 1110 0110 & 1 CP 1 1 0 0 ③同步置数法 预置数:D3D2D1D0=0011 预置信号

5.4 计数器 1 1 CP 1 0 0 1 0 ④进位C置数法 N=16,M=12,N-M=4 即 D3D2D1D0=0100

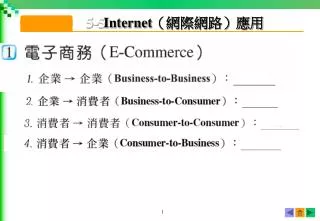

5.4 计数器 2.当M>N时:必须将多片计数器级联。 1)整体清“0”法或整体置数法 基本思路:先将n片计数器级联组成Nn(Nn>M)进制计数器,计满M个状态后,采用整体清“0”或整体置数法实现M进制计数器。 2)分解法 基本思路:将M=M1×M2×…Mn,其中M1、M2、…Mn均不大于N,则用n片计数器分别组成M1、M2、…Mn进制的计数器,然后级联即可构成M进制计数器。 芯片级联的方式: ①串行进位方式:以低位片的进位输出信号C作为高位片的时钟输入信号CP。 ②并行进位方式:以低位片的进位输出信号C作为高位片的工作状态控制信号EP和ET。

5.4 计数器 例:试用74160组成百进制计数器。 串行进位方式(异步计数器) 并行进位方式(同步计数器)

5.4 计数器 例:试用两片74160实现54进制计数器。 解:M=54,74160是具有异步清零、同步置数的十进制计数器。 5 3 ①整体置数法 Q3Q2Q1Q0 计数:0~53。 0 1 0 1 0 0 1 1