Process & Product checks

Learn about the importance of electrical testing in quality control at different stages of the process. Focus on parametric testing, product checks, and reliability processes. Understand process and test structures for efficient chip testing.

Process & Product checks

E N D

Presentation Transcript

Test Process & Product checks

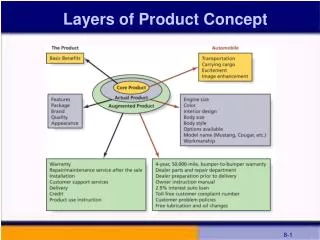

Introduction • Scope • Testing (quality control) is done at various steps • Our focus: Only electrical tests • Other tests: Defectivity test, etc • Electrical Testing • Process check (Only overall condition) • PARAMETRIC or E-Test • Product check (Pass/Fail for each chip) • BIN or SORT • RELIABILITY

Process Test (parametric) • Process Check • Simple structures, made between the ‘real’ chips • If the structures are very bad (all shorted, all open/ broken) • Chips are also likely to be ‘dead’ • Not worth processing further (if the wafers are in the midst of processing) • Not worth testing the chips (if the wafers have completed processing) • So, process check is done • in the ‘line’, at some standard steps (after M1 CMP and so on...) • and at the end, just before the chips are tested for pass/fail • The ‘simple structures’ used for process checks are normally called as ‘Scribe line’ or ‘Kerf’ • Process check is called “scribeline test’ or ‘kerf test’

Review from Mask: Basics • A mask may be 100 mm x 100 mm (for example) • So, one ‘print’ will be about 25 mm by 25 mm, on the wafer. • A chip may be only 5 mm by 4 mm • So, one mask will have perhaps 20 chips, if the chip is small • The gaps between the ‘real chips’ are used for • alignment marks (TBD) • test structures (TBD)

Process Test (parametric) • Basic check for shots/opens: • Metal lines: Snakes, Combs • Snake & Comb for both open and shorts • At each layer • Many structures • ==> many tests, time • few structures • ==> lower ability to predict fails • low resolution • if the snake is too long, cannot differentiate between real open vs marginal open vs good structure • if comb is too large, cannot distinguish between leakage vs shorts

Process Test (parametric) • Example of shorts: • What is expected in the electrical test © micro magazine • Very low resistance (or high leakage current) CDF plot Leak between combs Snake resistance

Process Test (parametric) • Plot of leakage current (CDF or QQ-Norm) • sorted values • log scale to identify ppm or ppb level defects • Stop processing the wafers with shorts/opens • Helps isolate problematic modules

Process Test (parametric) • VDP • Proximity structures • Kelvin • Misalign Structures • To find alignment margin • Border structures (via, contact) • Size structures • Capacitor (low-k specific) • intra layer • inter layer • Copper specific (Dishing/Erosion) • Concept of Short Loop, POR, split

Tester ©Advantest Ability to test at high temp some may have low temp capability also Die level vs package level

Probe ©Advantest Tungsten tip (for example) Auto probe vs Manual Probe

Test Program • C or script like • Normally well commented, reasonably readable • information on voltage applied (for example), store the data in test name etc.. • DUT (Device Under Test) • alignment and x,y movement • C-V test (for oxide) OR I-V results • time consuming • usually one result in a DUT in a die • TDDB, NBTI, ESD, EM • Summary file (for water, for lot ...) Temp. Dependent Dielectric Breakdown, Negative Bias Temperature Instability

Pads/Pins: Some examples Pads in product Test Pads in “test chip” and perhaps in scribe line Usually Parametric (analog) tester = slower Digital tester = faster Parallel testing => Faster even for parametric

Pads/Pins: Some examples Too long a pad-group ==> probe alignment/ probe contact issues Pads in “test chip” and perhaps in scribe line

Product Test • Binning • Soft bin, hard bin • initial stages, test the least failing part • some times COF • production stage, test the most failing part • always SOF • Continuity (leakage, open) • Built In Self Test (BIST) • Functional • SCAN • Memory • Repair (yield can improve dramatically) • Fail Bit Map (FBM) • WL ==> M1 short, BL fail ==> via fail (for example)

Product Test • IDDQ test ( Direct Drain Quiescent current) • some devices will pass the logic test, but will degrade in the field • likely to be captured by IDDQ test • Circuit must be CMOS and other parts must be isolated. Tested part should not give significant current, by design • (does not run at the specified frequency, so it won’t replace the function test, for example) • will not detect opens/ high resistance / interconnect capacitance effects • DC, AC, functional IDDQ... • QBD - charge (Q) to break down • Transistor (gate oxide) prob spec i