4-Bit Universal Shift Register

4-Bit Universal Shift Register. Behavioral Vs. Structural Description. Behavioral Description Behavior model of a shift register Describe the operation of the register without a preconceived structure. Random number generator Binary values of msb_in , lsb_in , i_par

4-Bit Universal Shift Register

E N D

Presentation Transcript

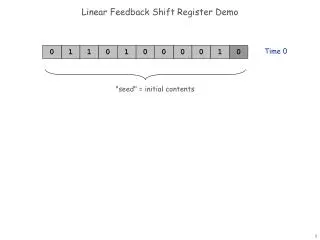

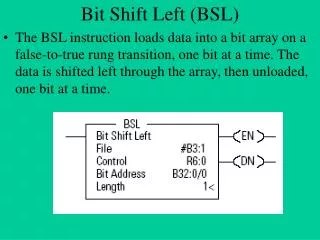

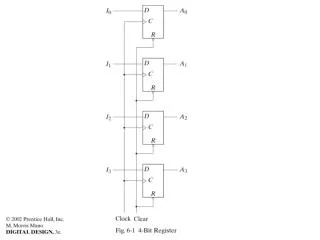

Behavioral Vs. Structural Description • Behavioral Description • Behavior model of a shift register • Describe the operation of the register without a preconceived structure. • Random number generator • Binary values of msb_in, lsb_in, i_par • Structural Description • Models the circuits in terms of a collection of components such as gates, flip-flops…

Test Bench 1. Generate random number With matlab Read random number at the neg edge of the clock

[s1,s0=[1,1], Load i_par=0111 a_par=0111

[s1,s0]=[0,0], No Change i_par=0111 a_par=0011

4-Bit Universal Shift Register Q clr clk select i3 i1 i0 i2

Waveform Load No Change Shift Right Shift Left