Logic Built in Self Test

380 likes | 747 Views

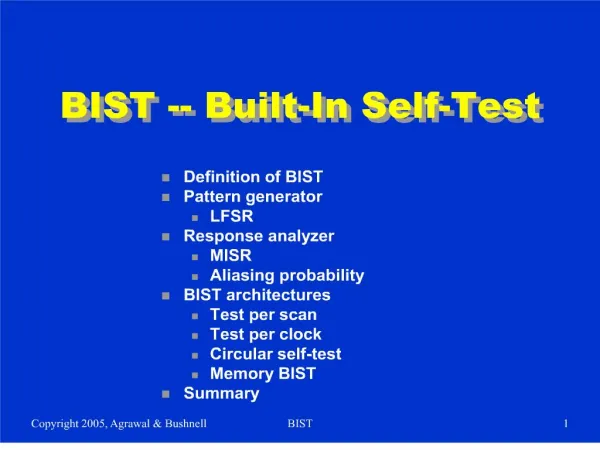

19 Jan 2004. BIST/ESG Seminar. 2. Plan. Introduction to TestingVarious testing techniquesBISTBIST and synthesisVarious approaches and algorithm suggestedConclusion. 19 Jan 2004. BIST/ESG Seminar. 3. Verification Vs Testing. VerificationDesign errorsTestingManufacturing defectsAging defects

Logic Built in Self Test

E N D

Presentation Transcript

1. 19 Jan 2004 BIST/ESG Seminar 1 Logic Built in Self Test Neeraj Goel

2002vls017

2. 19 Jan 2004 BIST/ESG Seminar 2 Plan Introduction to Testing

Various testing techniques

BIST

BIST and synthesis

Various approaches and algorithm suggested

Conclusion

3. 19 Jan 2004 BIST/ESG Seminar 3 Verification Vs Testing Verification

Design errors

Testing

Manufacturing defects

Aging defects

In-field regular testing is required

4. 19 Jan 2004 BIST/ESG Seminar 4 Fault models and Detection Gate level Stuck-at Fault model

Transistor level Stuck-at Fault model

Bridging Fault Model

Delay faults

5. 19 Jan 2004 BIST/ESG Seminar 5 Stuck at Fault model

6. 19 Jan 2004 BIST/ESG Seminar 6 Bridging Fault Models

7. 19 Jan 2004 BIST/ESG Seminar 7 Fault models and Detection Gate level Stuck-at Fault model

Transistor level Stuck-at Fault model

Bridging Fault Model

Delay faults

8. 19 Jan 2004 BIST/ESG Seminar 8 Testing Problem at Deep Sub-Micron Decreasing feature size

Low power supply

Increasing Number of pins

Test equipment cost

More test vectors

Increasing gate count

Memories, RF, MEMS on the chip

Different test methodologies

9. 19 Jan 2004 BIST/ESG Seminar 9 Various DFT methods Full scan

Boundary scan

Logic BIST

Quiescent current (IDDq test)

10. 19 Jan 2004 BIST/ESG Seminar 10 Scanning

11. 19 Jan 2004 BIST/ESG Seminar 11 Scanning

12. 19 Jan 2004 BIST/ESG Seminar 12 Scan Design Techniques Flip-flop of design? Scan registers

Use of Multiplexer

Increased controllability and observability

Two step synthesis approach: scan mode and scan chain connection are done at second step

Special scan registers

13. 19 Jan 2004 BIST/ESG Seminar 13 Full scan Additional wiring and mux : area and performance effect

Long test time

Less effort in ATPG

Cost increases with number of pins.

14. 19 Jan 2004 BIST/ESG Seminar 14 Full Scan (cont.) To prevent the problem other alternatives

Multiple scan chains

Partial scan design

15. 19 Jan 2004 BIST/ESG Seminar 15 Boundary Scan Use reduced number of pins

Less cost of tester

Need scannble latches at non-test I/O

Additional cost of Mux (Performance)

Large handling capabilities of ATPG system required

16. 19 Jan 2004 BIST/ESG Seminar 16 IDDQ test Relatively cheap

Time require for each pattern is long

Very convenient for bridge faults

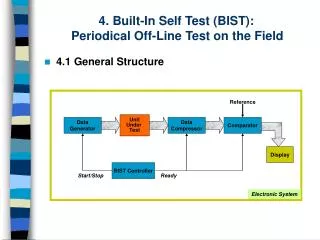

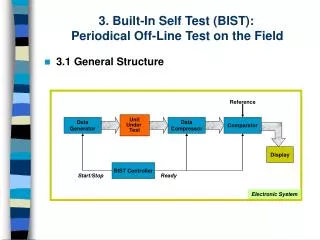

17. 19 Jan 2004 BIST/ESG Seminar 17 Basic BIST Architecture

18. 19 Jan 2004 BIST/ESG Seminar 18 Advantages of BIST Can be used at all level of testing

System level testing in field

At speed testing

No need for external test machines

Less I/O pins needed for testing

Burn-in Test made easy

No need for test vector development

19. 19 Jan 2004 BIST/ESG Seminar 19 Disadvantages of BIST Area overhead

-more susceptibility to manufacturing defects

Performance penalties

Designing and verifying proper operation of BIST at design level.

Additional risk in project

20. 19 Jan 2004 BIST/ESG Seminar 20 Traditional LBIST architecture- STUMPS Self-testing using MISR and parallel shift (Stumps)

PRPG generate input for internal scan chains

Compress the response in MISR

Linear Feedback Shift Register (LFSR) generate pseudo random pattern.

21. 19 Jan 2004 BIST/ESG Seminar 21 Traditional LBIST architecture- STUMPS

22. 19 Jan 2004 BIST/ESG Seminar 22 Built-in Logic Block Observer

23. 19 Jan 2004 BIST/ESG Seminar 23 Concurrent BILBO

24. 19 Jan 2004 BIST/ESG Seminar 24

25. 19 Jan 2004 BIST/ESG Seminar 25 BIST and Synthesis Circuit optimization for test

Incomplete information available => use estimation

Goal:

Test concurrency

Minimum area overhead

26. 19 Jan 2004 BIST/ESG Seminar 26 High level synthesis approach GOAL: test concurrency

Issues involved: Hardware conflicts

Probable Solution: Choose the data path such that less conflicts

27. 19 Jan 2004 BIST/ESG Seminar 27 Synthesis stages Data-flow Scheduling for Testability

Binding for Testability

Test concurrency matrix

Test Register Selection

Incremental approach

Test Path Definition

Test point insertion

Test Scheduling

28. 19 Jan 2004 BIST/ESG Seminar 28 SyncBIST Test Synthesis Overview

29. 19 Jan 2004 BIST/ESG Seminar 29 Some Experimental Results

30. 19 Jan 2004 BIST/ESG Seminar 30 Another approach-by Gonzalez et al Minimizing testability cost and time by

- multiple concurrent test sessions

- register sharing

31. 19 Jan 2004 BIST/ESG Seminar 31 Algorithm[1] Preprocessing

Built compatibility graphs of the FUs

Built test status Matrix and call the cost function

Apply minimal register allocation procedure

32. 19 Jan 2004 BIST/ESG Seminar 32 Yang and Muzio�s Approach[3] Module allocation and register allocation are performed incrementally

-Module allocation is guided by testability balance technique

-Register allocation aims at increasing the sharing degree

33. 19 Jan 2004 BIST/ESG Seminar 33 Algorithm Perform default allocation

For all normal registers do

Do life time analysis of variables

end for

For all register do

Change to register according to functionality

end for

Repeat

Perform module allocation

Perform test register allocation

for all normal register do

Estimate the incremental hardware cost

end for

Select pair with smallest cost

Merge the select pair and change the data path and registers accordingly.

until no merger exist

34. 19 Jan 2004 BIST/ESG Seminar 34 Experimantal Results

35. 19 Jan 2004 BIST/ESG Seminar 35

36. 19 Jan 2004 BIST/ESG Seminar 36 Conclusion At deep submicron test cost and test time are major issues to be considers

BIST can be a good option in this scenario

To ensure good test performance, it is necessary to estimate the quality of test behavior during synthesis.

37. 19 Jan 2004 BIST/ESG Seminar 37 Reference J A Q Gonzalez, J R Amazonas, M Strum, W J Chau, �Self Test Built-in plan for Data-Path Functional Units� IEEE Latin American Test Workshop, 2000.

A Orailoglu, G Harris, �Microacritectural Synthesis for Rapid BIST Testing�, IEEE trans. On CAD of ICS, June 1997

L T Yang, J Muzio, �Built in Self Testable Data Path Synthesis� , In proc. Of IEEE Int. conf. On VLSI, April 2001.

C Feige, M j Geuzebroek, �Logic BIST technology evalution: an industrial case study�, European test workshop 2001.

Charles E. Strode, �A Designers guide to Built-in Self-test�, Kluwer Academic Publisher,2002.