PROGRAMMABLE LOGIC DESIGN WITH VHDL

PROGRAMMABLE LOGIC DESIGN WITH VHDL. Objectives. Upon completion of this training, your VHDL knowledge will enable you to: Implement efficient combinatorial and sequential logic Design state machines and understand implementation trade-offs Use hierarchy / Create reusable components

PROGRAMMABLE LOGIC DESIGN WITH VHDL

E N D

Presentation Transcript

Objectives • Upon completion of this training, your VHDL knowledge will enable you to: • Implement efficient combinatorial and sequential logic • Design state machines and understand implementation trade-offs • Use hierarchy / Create reusable components • Identify how VHDL will synthesize and fit into a PLD, CPLD and FPGA

Objectives (contd.) • Upon completion of this training, you will be able to use Warp to: • Compile and synthesize VHDL designs for programmable logic devices • Create VHDL or Verilog timing simulation models for popular third party simulators. • Target PLDs/CPLDs • Simulate the resulting device with the Aldec full timing simulator • Use the report file to determine operating frequency, set-up time, clock to output delay, and device resource usage.

Intro, Why Use VHDL?, Design Flow VHDL Design Descriptions The Entity, Ports, Modes, Types Exercise #1 - Write an entity statement The Architecture, differing styles Concurrent and Sequential statements Processes: Signals vs. Variables VHDL Operators/Overloading/Inferencing VHDL Identifiers Exercise #2 - write an architecture Tri-State Logic, Don't Cares Warp GUI overview Exercise #3 - Design a bus controller Aggregates and Subscripts Registers, Latches and Implicit Memory Exercise #4 - Design a counter Lunch State Machines and State Encoding Exercise #5 - Design a state machine Design Hierarchy - components, pkg’s, libraries Exercise #6 - Design a loadable counter hierarchy Generate Statement Multiplexing I/O pins Exercise #7 - DRAM output controller User defined attributes CPLD synthesis directives Miscellaneous Topics and Wrap-up Agenda

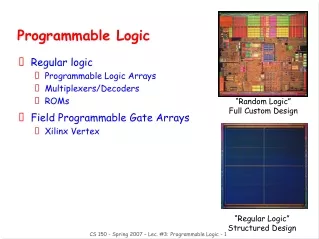

Introduction • VHDL is used to: • document circuits • simulate circuits • synthesize design descriptions • Synthesis is the reduction of a design description to a lower-level representation (such as a netlist or a set of equations). • This training course covers VHDL for PLD synthesis • The course will at times draw upon the concepts of VHDL as a simulation language

Why Use VHDL? • Quick Time-to-Market • Allows designers to quickly develop designs requiring tens of thousands of logic gates • Provides powerful high-level constructs for describing complex logic • Supports modular design methodology and multiple levels of hierarchy • One language for design and simulation • Allows creation of device-independent designs that are portable to multiple vendors. Good for ASIC Migration • Allows user to pick any synthesis tool, vendor, or device

Developed by DoD in early 80s as means for Contractors to Describe Designs-Funded VHSIC 1987 IEEE ratified 1076 and DoD mandated VHDL(F-22) and EDA vendors created tools. 1993 - IEEE 1076 ‘93 1996 Commercial Sim and Synthesis tools become available and 1164 pkg enables multi value logic 1983 -Gateway founded by Genrad’s HDL and HILO simulator author.Releases Verilog HDL and Simulator 1985 Enhanced Verilog-XL-used for high end designs -Fast Simulator - interpretive-no need to precompile 1990 Cadence buys Gateway-nearly all ASIC foundries used XL as Golden Simulator 1995 IEEE 1364 VHDL vs. Verilog History

Many E-A pairs may reside in single system file. User Can define Data Types-Powerful High Level Modeling w/ Package, Config, Generate Strongly Typed Language - models must be precisely coded-often longer code Less intuitive but much more powerful constructs Order or Code is crucial to obtaining desired output. Simple Data Types are controlled by language No Equivalent High Level Modeling Constructs Verilog has looser structure-can lead to unwanted and unidentified errors-more concise code. Easiest to Grasp-more prone to create unwanted results VHDL vs. VerilogCompilation/Data Types/High Level Constructs/Verbosity/Ease

WARP5.0 • WARP2 Release 5.0 now supports Verilog Synthesis • Same great Synthesis as VHDL • Includes Aldec Full Timing Simulator and FSM Editor • Generates timing simulation models for major third party VHDL and Verilog simulators • New GUI-Microsoft Std Interface • Even Better HDL Editor • Supports All Cypress Devices • Windows 95, NT, UNIX • Same Great $99 Price

Fitting Sim. Model Simulator JAM file JEDEC ISR/Impulse3 Warp2/Warp3/Programming Design Entry Schematic Text/FSM Front End Simulation Synthesis Design Compilation Back End Design Verification

VHDL Design Descriptions • VHDL design descriptions consist of an ENTITY declaration and an ARCHITECTURE body • The ENTITY declaration describes the design I/O • The ARCHITECTURE body describes the content or function of the design • Every architecture needs an entity so it is common to refer to them together as an ENTITY/ARCHITECTURE PAIR

Example Entity/Architecture Pair:A 2-Input And Function ENTITY and2 IS PORT ( a,b : IN std_logic; f: OUT std_logic); END and2; ARCHITECTURE behavioral OF and2 IS BEGIN f <= a AND b; END behavioral;

The Entity • A “BLACK BOX” • The ENTITY describes the periphery of the black box (i.e., the design I/O) BLACK_BOX rst q[7:0] d[7:0] co clk

BLACK_BOX rst q[7:0] d[7:0] co clk Example Entity declaration ENTITY black_box IS PORT ( clk, rst: INstd_logic; d: INstd_logic_vector(7 DOWNTO 0); q: OUTstd_logic_vector(7 DOWNTO 0); co: OUTstd_logic); END black_box; • What does all this mean?

The Entity Declaration ENTITYentity_name IS -- optional generics PORT ( name : mode type ; ... ) ; ENDentity_name; • entity_name is an arbitrary name • generics are used for defining parameterized components • name is the signal/port identifier and may be a comma separated list for ports of identical modes and types • mode describes the direction the data is flowing • type indicates the set of values name may be assigned

Ports • The Entity (“BLACK BOX”) has PORTS • PORTS are the points of communication • PORTS are usually the device pins • PORTS have an associated name, mode, and type

Entity Port Modes A port’s MODE indicates the direction that data is transferred: • IN Data goes into the entity only • OUT Data goes out of the entity only (and is not used internally) • INOUT Data is bi-directional (goes into and out of the entity) • BUFFER Data that goes out of the entity and is also fed-back internally

IEEE 1076 Types • VHDL is a strongly typed language (you cannot assign a signal of one type to the signal of another type) • bit - a signal of type bit that can only take values of '0' or '1' • bit_vector - a grouping of bits (each can be '0' or '1') SIGNAL a: BIT_VECTOR(0 TO 3); -- ascending range SIGNAL b: BIT_VECTOR(3 DOWNTO 0); -- descending range a <= "0111"; -- double quotes used for vectors b <= "0101"; This means that: a(0) = '0' b(0) = '1' a(1) = '1' b(1) = '0' a(2) = '1' b(2) = '1' a(3) = '1' b(3) = '0'

IEEE 1076 TYPES (contd.) • INTEGER • useful as index holders for loops, constants, generics, or high-level modeling • BOOLEAN • can take values ‘TRUE’ or ‘FALSE’ • ENUMERATED • has user defined set of possible values, e.g., • TYPE traffic_light IS (green, yellow, red);

IEEE 1164 • A package created to solve the limitations of the BIT type • Nine values instead of just two ('0' and '1') • Allows increased flexibility in VHDL coding, synthesis, and simulation • STD_LOGIC and STD_LOGIC_VECTOR are used instead of BIT and BIT_VECTOR when a multi-valued logic system is required • STD_LOGIC and STD_LOGIC _VECTOR must be used when tri-state logic (Z) is required • To be able to use this new type, you need to add 2 lines to your code: LIBRARY ieee; USE ieee.std_logic_1164.ALL;

1164 Types • std_logic and std_logic_vector are the industry standard logic type for digital design • Values for Simulation & Synthesis • ‘0’ -- Forcing ‘0’ • ‘1’ -- Forcing ‘1’ • ‘Z’ -- High Impedance • ‘L’ -- Weak ‘0’ • ‘H’ -- Weak ‘1’ • ‘-’ -- Don’t care • Values for Simulation only (std_ulogic): • ‘U’ -- Uninitialized • ‘X’ -- Forcing Unknown • ‘W’ -- Weak Unknown

BLACK_BOX MODE rst TYPE q[7:0] d[7:0] co clk Entity Declaration Example LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY black_box IS PORT ( clk, rst: INstd_logic; d: INstd_logic_vector(7 DOWNTO 0); q: OUTstd_logic_vector(7 DOWNTO 0); co: OUTstd_logic); END black_box;

Exercise #1: The Entity - A Walk through • Write an entity declaration for the following: Port D is a 12-bit bus, input only Port OE and CLK are each input bits Port AD is a 12-bit, three-state bi-directional bus Port A is a 12-bit bus, output only Port INT is a three-state output Port AS is an output also used internally my_design ad[11:0] d[11:0] a[11:0] oe int clk as

my_design ad[11:0] d[11:0] a[11:0] oe int clk as Exercise #1: Solution LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY my_design IS PORT ( d: IN std_logic_vector(11 DOWNTO 0); oe, clk: IN std_logic; ad: INOUT std_logic_vector(11 DOWNTO 0); a: OUT std_logic_vector(11 DOWNTO 0); int: OUT std_logic; as: BUFFER std_logic); END my_design; -- In this presentation, VHDL keywords -- are highlighted in bold, CAPITALS; -- however, VHDL is not case sensitive: -- clock, Clock, CLOCK all refer to the -- same signal, -- means a comment

The Architecture • Architectures describe what is in the black box (i.e., the structure or behavior of entities) • Descriptions can be either a combination of • Structural descriptions • Instantiations (placements of logic-much like in a schematic-and their connections) of building blocks referred to as components • Behavioral/Dataflow descriptions • Algorithmic (or “high-level”) descriptions: IF a = b THEN state <= state5; • Boolean equations (also referred to as dataflow): x <= a OR (b AND c);

The Architecture Declaration ARCHITECTURE arch_name OFentity_name IS -- optional signal declarations, etc. BEGIN --VHDL statements ENDarch_name; • arch_name is an arbitrary name • optional signal declarations are used for signals local to the architecture body (that is, not the entity’s I/O). • entity_name is the entity name • statements describe the function or contents of the entity

Architecture Body Styles : Behavioral ENTITY compare ISPORT ( a, b: IN std_logic_vector(0 TO 3); equals: OUT std_logic); END compare; ARCHITECTURE behavior OF compare IS BEGIN comp: PROCESS (a,b) BEGIN IF a = b THEN equals <= '1' ; ELSE equals <= '0' ; ENDIF ; ENDPROCESS comp; END behavior;

Architecture Body Styles : Dataflow ENTITY compare ISPORT ( a, b: IN std_logic_vector(0 TO 3); equals: OUT std_logic); END compare; ARCHITECTURE dataflow OF compare IS BEGIN equals <= '1' WHEN a = b ELSE '0' ; END dataflow;

Architecture Body Styles : Structural ENTITY compare ISPORT ( a, b: IN std_logic_vector(0 TO 3); equals: OUT std_logic); END compare; USEWORK.gatespkg.ALL ; ARCHITECTURE structure OF compare IS SIGNAL x : std_logic_vector (0 to 3) ; BEGIN u0: xnor2 PORTMAP (a(0),b(0),x(0)) ; u1: xnor2 PORTMAP (a(1),b(1),x(1)) ; u2: xnor2 PORTMAP (a(2),b(2),x(2)) ; u3: xnor2 PORTMAP (a(3),b(3),x(3)) ; u4: and4 PORTMAP (x(0),x(1),x(2),x(3),equals) ; END structure;

LOGIC a d b f c Mixing Architecture Styles • The various styles may be mixed in one architecture. ENTITY logic IS PORT ( a,b,c: IN std_logic; f: OUT std_logic); END logic; USE WORK.gatespkg.ALL; ARCHITECTURE archlogic OF logic IS SIGNAL d: std_logic; BEGIN d <= a AND b; g1: nor2 PORT MAP (c, d, f); END archlogic; g1 Behavioral/Dataflow Structural

Comparing Architecture Styles • These examples synthesize to equivalent circuits • In more elaborate designs, some descriptions may yield more efficient circuits • sloppy code = inefficient results (see section 3.3.4) • Use styles that make your designs easier to describe and maintain • Behavioral/Dataflow exploit module generation (described later) • Structural descriptions may make the design less portable (may rely on a library of vendor-specific components)

Module Generation • In Warp release 4.0, a package called ‘std_arith’ can be used to overload the arithmetic (+, -, etc.) and relational operators (=, /=, <, etc.,) for std_logic, std_logic_vector and integer types • Using this package causes adders, counters, comparators, etc., to automatically replace the operators in the design. These are optimized for the target architecture and synthesis goal (area/speed) • This is known as module generation

Speed Area Speed Area Speed Area Adders Subtractors Multipliers Comparators Counters Shifters Adders Subtractors Multipliers Comparators Counters Shifters Ultra39000 Adders Subtractors Multipliers Comparators Counters Shifters Adders Subtractors Multipliers Comparators Counters Shifters Adders Subtractors Multipliers Comparators Counters Shifters Adders Subtractors Multipliers Comparators Counters Shifters FLASH370i Ultra39000 Ultra37000 FLASH370i Ultra37000 Ultragen Synthesis The VHDL code below describes a comparator Pre-optimized Circuits if (a = b) then c <= ‘1’; else c <= ‘0’; end if; Warp chooses the best pre-optimized circuit to meet your design goals

count clk A Simple Counter LIBRARY ieee; USE ieee.std_logic_1164.ALL; USEWORK.std_arith.ALL; ENTITY count8 ISPORT ( clk: IN std_logic; count: BUFFER std_logic_vector(7 DOWNTO 0)); END count8 ; ARCHITECTURE arch_count8 OF count8 IS BEGIN upcount: PROCESS (clk) BEGIN IF clk’EVENT and clk=‘1’ THEN count <= count + 1; END IF; END PROCESS upcount; END arch_count8;

VHDL Statements • There are two types of statements, Concurrentand Sequential • Concurrent Statements(means in parallel) • Concurrent statements are “executed” concurrently (at the same time) • The order of concurrent statements is not important • Most of the examples we have seen so far have been concurrent statements: • Boolean Equations • WHEN-ELSE • WITH-SELECT-WHEN

VHDL Statements (cont.) • Sequential Statements(means in series) • Sometimes we need to model complex functions. In that case, we can use an “algorithm” or model to describe the function. This is done with Sequential Statements • With Sequential statements, the ORDER of the statements is important (example later) • Therefore, we use aprocessto mark the beginning and end of a block of sequential statements • Each completed process is considered to be one big concurrent statement (there can be many processes inside one architecture)

What is a VHDL “Process” ? • Processes are either awake or asleep (active or inactive) • A process normally has a sensitivity list • When a signal in that sensitivity list changes value, the process wakes up and all of the sequential statements are “executed” • For example, a process with a clock signal in its sensitivity list will become active on changes of the clock signal • At the end of the process, all outputs are assigned and the process goes back to sleep until the next time a signal changes in the sensitivity list

The Process (contd.) label: PROCESS (sensitivity list) -- variable declarations BEGIN -- sequential statements END PROCESS label ; • The process label and variable declarations are optional • The process executes when one of the signals in the sensitivity list has an event

Combinational Logic • Can be described with concurrent statements • boolean equations • when-else • with-select-when • component instantiatons • Can be described with sequential statements • if-then-else • case-when

Combinational Logic w/ Boolean Equations • Boolean Equations can be used in both concurrent and sequential signal assignment statements. • A 4-1 multiplexer is shown below x <= (a AND NOT(s(1)) AND NOT(s(0))) OR (b AND NOT(s(1)) AND s(0)) OR (c AND s(1) AND NOT(s(0))) OR (d AND s(1) AND s(0)) ; s 2 a x b mux c d

Selective Signal Assignment:with-select-when • Assignment based on a selection signal • WHEN clauses must be mutually exclusive • Use a WHEN OTHERS when all conditions are not specified • Only one reference to the signal, only one assignment operator (<=) WITH selection_signal SELECT signal_name <= value_1 WHEN value_1 of selection_signal, value_2 WHEN value_2 of selection_signal, ... value_n WHEN value_n of selection_signal, value_x WHEN OTHERS;

Combinational Logic w/ Selective Signal Assignment • The same 4-1 multiplexer is shown below with s select x <= a when “00” , b when “01” , c when “10” , d whenothers ; s 2 a x b mux c d

More on with-select-when • You can use a range of values with int_value select x <= a when 0 to 3, b when 4 | 6 | 8 , c when 10 , d whenothers ;

Conditional Signal Assignment:when-else • Signal is assigned a value based on conditions • Any simple expression can be a condition • Priority goes in order of appearance • Only one reference to the signal, only one assignment operator (<=) • Use a final ELSE to avoid latches signal_name <= value_1 WHEN condition1 ELSE value_2 WHEN condition2 ELSE ... value_n WHEN condition N ELSE value_x ;

Combinational Logic w/ Conditional Signal Assignment • The same 4-1 multiplexer is shown below x <= a when (s = “00”) else b when (s = “01”) else c when (s = “10”) else d ; s 2 a x b mux c d

Combinational Logic w/ Conditional Signal Assignment • The when conditions do not have to be mutually exclusive (as in with-select-when) • A priority encoder is shown below j <= w when (a = ‘1’) else x when (b = ‘1’) else y when (c = ‘1’) else z when (d = ‘1’) else “000” ;

Combinatorial Logic w/ Sequential Statements • Grouped together with Processes • Processes are concurrent with one another and with concurrent statements • Order of sequential statements does make a difference in synthesis

Sequential Statements: if-then-else • Used to select a set of statements to be executed • Selection based on a boolean evaluation of a condition or set of conditions • Absence of ELSE results in implicit memory IF condition(s) THEN do something; ELSIF condition_2 THEN -- optional do something different; ELSE -- optional do something completely different; END IF ;

if-then-else • 4-1 mux shown below mux4_1: process (a, b, c, d, s) begin if s = “00” then x <= a ; elsif s = “01” then x <= b ; elsif s = “10” then x <= c ; else x <= d ; end if; end process mux4_1 ; s 2 a x b mux c d

Sequential Statements: Case-When CASE selection_signal IS WHEN value_1_of_selection_signal => (do something) -- set of statements 1 WHEN value_2_of_selection_signal => (do something) -- set of statements 2 ... WHEN value_N_of_selection_signal => (do something) -- set of statements N WHEN OTHERS => (do something) -- default action END CASE;