Programmable Logic System Design

240 likes | 258 Views

Programmable Logic System Design. Lab03- Simulation Preliminary SOC LAB . 2019.10.17. Lab Description. 認識實驗版 撰寫 VHDL ,利用 Switch 模組控制 LED 模組 定義 I/O 腳位 (I/O Pins) ,產生燒錄檔 (*.sof) ,燒錄並觀察在 FPGA 板子上的結果. Altera Cyclone II DE2-70 FPGA board. Create Xilinx Project.

Programmable Logic System Design

E N D

Presentation Transcript

Programmable Logic System Design Lab03- Simulation Preliminary SOC LAB. 2019.10.17

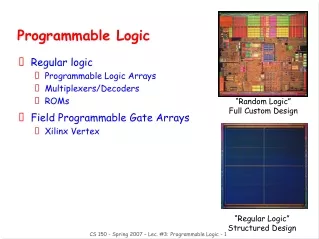

Lab Description • 認識實驗版 • 撰寫 VHDL,利用 Switch 模組控制 LED 模組 • 定義I/O腳位(I/O Pins),產生燒錄檔(*.sof),燒錄並觀察在 FPGA 板子上的結果

Create Xilinx Project • 若忘記 Quartus II 開新 Project 的設定請參考 Lab1 的講義

Use Switches to Light LEDs library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity lab3 is Port ( iSW : in std_logic_vector(9 downto 0); oLEDR : out std_logic_vector(9 downto 0)); end lab3; architecture Behavioral of lab3 is begin oLEDR(9 downto 0) <= iSW(9 downto 0); end Behavioral;

Pin Assignment • Open Pin planner

Pin Assignment (Cont’d) • Check pin assignment

Program the DE1-SOC Board(Cont’d) • Open Hardware Setup

Program the DE1-SOC Board(Cont’d) • Select hardware as USB-Blaster [USB-0]

Program the DE1-SOC Board(Cont’d) • Select auto Detect

Program the DE1-SOC Board(Cont’d) • Change file

Program the DE1-SOC Board(Cont’d) • Select your file (*.sof )

Program the DE1-SOC Board(Cont’d) • Start program

Program the DE1-SOC Board(Cont’d) • Program success

Assignment • 以VHDL 撰寫描述此一真值表並完成波形模擬圖、腳位設定以及Download。並輸入訊號觀察與模擬設計是否相符。

Right click “USB-Blaster” and select setup driver. Then select “install from a list or specific location”.

Choose the file from C:\altera\13.0sp1\quartus\drivers\usb-blaster and install.