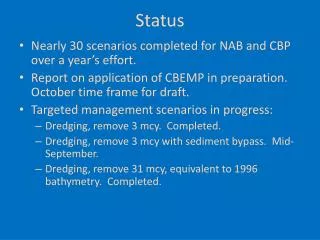

HR3 status

HR3 status. AIDA WP9.5: MILESTONES and SCHEDULE. Schedule presented at the AIDA Kick Off meeting 2011: Characterization of the 2 nd generation ROC Chips Dedicated run produced in March 2010 25 wafers received in June 20 000 chips packaged in the US

HR3 status

E N D

Presentation Transcript

AIDA WP9.5: MILESTONES and SCHEDULE • Schedule presented at the AIDA Kick Off meeting 2011: Characterization of the 2nd generation ROC Chips • Dedicated run produced in March 2010 • 25 wafers received in June • 20 000 chips packaged in the US 2012Feb 2013: Submission and test of one of the 3rd generation chips 20132014 ?: Submission of a second 3rd generation chip August 2013: Report • Budget for 3rd generation of electronics: • 31k€ (ECAL) + 50 k€ (Hadronic Calorimeter) => 2 chip submissions • 30 ppm • Cost: • Multi Project runs (MPW): 1k€/mm2 • Packaging: $3500 • Testboard: 1500 € HARDROC2/MICROROC SDHCAL RPC/µMEGAS 64 ch 20 mm2/ SKIROC2 ECAL Si 64 ch. 65 mm2 SPIROC2 AHCAL SiPM 36 ch 32 mm2 0.35µm SiGe AMS technology May 2013

AIDA WP9.5: 3rd generation of ROC chips Slave address S R A data A P Slave address Slave address S S W W A A Reg address Reg address A data A A P P • 2nd generation ROC chip • Auto-trigger, analog storage, digitization and token-ring readout, common DAQ • Power pulsing : <1 % duty cycle • 3rd generation ROC chip • Independent channels (= Zero suppress) • 64/36 address pointers • ReadOut, BCID, SCA (Spiroc and Skiroc) management => Digital part much more complicated • SCA depth: 8 instead of 16 • Possibility to use “Roll mode” by Slow Control: circular memory very useful for Testbeam • New TDC with no dead time • New Slow Control (Triple voting) using I2C link (while keeping the « old SC » system) Master Slave 1 Slave 2 Slave 3 Slave x Clock Data I2C link May 2013

HARDROC2 • 64 channels (RPC SDHCAL) • preamp + shaper+ 3 discris (semi digital readout) • Auto trigger on 10fC up to 20 pC • 5 0.5 Kbytes memories to store 127 events • Full power pulsing => 7.5 µW/ch • 2010 TB : 1 m2 (144 HR2b) • power pulsing in magnetic field successfully tested • SDHCAL technological proto with 40 layers (5760 HR2 chips) built in 2010-2011. • Testbeam summer 2011: pb with the DAQ2 (HDMI) + pb of cooling • TB November 2011: 6 detectors and USB DAQ: good performance of the electronics and detector • TBs 2012 with 40 detectors and intermediate DAQ (HDMI & DCC cards for synchronization and USB for config & readout) Very good TB results with a complete system, autotrigger mode, power pulsing • HARDROC3 FE: No major modifications needed Cosmic hadronic shower X Z Y X Blue : 150 fC Green : 2 pC Red : 18 pC Y Z @IPNL May 2013

HARDROC3 • No major modifications needed in the FE • submittedat the end of Feb 2013 (SiGe 0.35µm), expected in June 2013 • Die size ~30 mm2 (6.3 x 4.7 mm2) • To be packaged in a TQFP208 • 64 independent channels • I2C link (@IPNL) • PLL: integratedbefore in a builiding block, first measurements are very good • Input frequency 2.5 MHz =>output frequency: 10, 20, 40, and 80 MHz available • Bandgap: new one with a better temperature sensitivity, tested in a building block • Temperature sensor: tested in a building block, slope – 6mV/°C • Test board to be designed • 2013: dedicated to the test of HR3 before submitting other chips May 2013

Building blocks (integrated in HR3): results • In parallel, small building blocks weredesigned and submitted in 2012, received and tested in February 2013 • Bandgap (5 chips): • Temperaturesensitivity: ~70 µV/°C (was 250 µV/°C with the previous BG) • Non uniformitybetween chips depends on the uniformity of the reference voltages which are referred to a 2.5V generated by a bandgap: Vbg Uniformity (30°C): < 14 mV (was 20 mV in hardroc2) • Temperature sensor: -6mV/°C • PLL: to generate clocks internally. Firstmeasurements are very good • Input frequency 2.5 MHz =>output frequency: 10, 20, 40, and 80 MHz available PLL @D. Thienpont May 2013

SUMMARY • Nice TB results obtained with HARDROC2b chips, in AUTOTRIGGER mode • Complete system, large dynamic range, low noise • Tests with power pulsing mode • End of Feb 2013: submission of HARDROC3 • Semi digital readout => « Simple » chip compared to Skiroc and Spiroc: I2C, independent channels, circular memory, one register/channel, temperature sensor • package: TQFP208 instead of TQFP 160 for HR2 • New 2-3 m RPC chambers to be built to test HR3 at the system level • Die size ~30 mm2 => 30 k€ + 5K test setup (AIDA funding) + 16 ppm/30 ppm used • Tests should start at this summer (depending on the testboard design) May 2013

BACK UP Slides May 2013

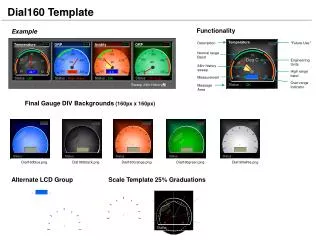

3Gen ROC chips: common features • DIF sequencing (Acq, Conv and Readout): • Backward compatibility with 2Gen ROC chips sequencing • Use of ChipSat signal • Daisy chained chips for readout • Possibility to use Roll mode by Slow Control: • If RollMode = “0” Backward compatibility with 2Gen ROC chips behavior • Only the N first events are stored • If RollMode = “1” 3Gen ROC chips behaviour • Use the circular memory mode • Only the N last events are stored May 2013

3Gen ROC chips: common features Slave address S R A data A P Slave address Slave address S S W W A A Reg address Reg address A data A A P P • Slow control parameters: • Backward compatibility with 2Gen ROC chips slow control • Use of classical shift register slow control • Embedded I2C • 7-bit address + 1 general call address (127 chips can be addressed) • Access port doubled • Bidirectional data line with open collector (Driver will be the same as Dout) • Read back capability of SC bits (non destructive) Master Slave 1 Slave 2 Slave 3 Slave x Clock Data • Write frame: • Read frame: May 2013

3Gen ROC chips: common features • Extra pin needed for I2C / SC: Standard SC SC with triple voting I2C Selection I2C or std SC May 2013