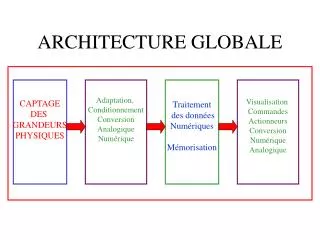

ARCHITECTURE GLOBALE

ARCHITECTURE GLOBALE. CAPTAGE DES GRANDEURS PHYSIQUES. Adaptation, Conditionnement Conversion Analogique Numérique. Traitement des données Numériques Mémorisation. Visualisation Commandes Actionneurs Conversion Numérique Analogique. LE SYSTEME MINIMUM. Programme. Données.

ARCHITECTURE GLOBALE

E N D

Presentation Transcript

ARCHITECTURE GLOBALE CAPTAGE DES GRANDEURS PHYSIQUES Adaptation, Conditionnement Conversion Analogique Numérique Traitement des données Numériques Mémorisation Visualisation Commandes Actionneurs Conversion Numérique Analogique

LE SYSTEME MINIMUM Programme Données Mémoire Non Volatile EPROM, EEPROM Mémoire Vive (RAM) MICROPROCESSEUR CS A0 à AnD0 à Dn CS A0 à AnD0 à Dn Bus d’adresse Bus de données Interface d’entrée/Sortie Décodage d’adresse

Bus de données Le Microprocesseur: Architecture interne Registres de travail Accumulateurs Registres d’adressage PC, Index, pointeur De piles Registre d’état BUS ADRESSE UAL Registres D’instructions Circuits séquencement Interne et contrôle de commande Quartz Circuit d’horloge Les lignes de commandes

0 1 0 0 1 1 0 0 LES BUS : GENERALITES DEFINITION: Ensemble de lignes destinées au transport d’informations binaires dont le format correspond au nombre de fils du bus. Exemple : bus de données 8 bits D0 à D7 L’information est disponible en parallèle: Chaque bit du mot binaire est disponible au simultanément . Mot binaire transporté : 4C(hexa)

Les bus du microprocesseur Le bus des données: permet d’échanger des informations binaires entre le microprocesseur et les circuits périphériques Lecture Écriture

Les bus du microprocesseur 2 Le bus des adresses: permet de choisir la case mémoire du circuit périphérique qui contient l’information que le microprocesseur veut lire ou modifier Capacité d’adressage de la mémoire: 213 adresses (8Ko) Le microprocesseur impose l’adresse Capacité d’adressage du microprocesseur: 216 adresses (64Ko)

Les bus du microprocesseur 3 Le bus de commande: ensemble de signaux permettant au système (microprocesseur et périphériques) de fonctionner Signaux de commandes entrants depuis les périphériques Signaux de commandes sortants vers les périphériques

Le µp 6809 : structure « logicielle » Les différents registres et leur format b 7 b0 b7 b 0 A B Accumulateurs A et B 8 bits b15 D b 0 ou D registre de 16 bits 15 X 0 Registre d’index X de 16 bits 15 Y 0 Registre d’index Y de 16 bits 15 U 0 Pointeur de pile utilisateur 15 S 0 Pointeur de pile système 7 DP 0 Registre d’adresse de page 15 PC 0 compteur programme 7 CCR 0 Registre d’état

Instruction : Format et caractéristiques Pour chaque microprocesseur le code définissant l’instruction à un format spécifié. Pour le 6809, deux champs obligatoires : code opération et opérande PREMIER CHAMPDEUXIEME CHAMP CODE OPERATIONOPERANDE 1 Octet1 ou 2 octets Exemple : LDA$C007 Les deux caractéristiques essentielles sont la durée en nombre de cycles machines et la taille en octets

Instruction : Mécanisme d’exécution 1ère étape Le PC contient l’adresse de l’instruction à exécuter.

Instruction : Mécanisme d’exécution 2ème étape La donnée contenu dans la case mémoire dont l’adresse était pointé par le PC est transférée dans le registre d’instruction pour y être décodée

U? 39 8 A0 X1 A0 9 A1 A1 10 A2 A2 38 11 A3 EX2 A3 12 A4 A4 37 13 A5 RESET A5 2 14 A6 NMI A6 15 A7 A7 40 16 A8 HALT A8 3 17 A9 IRQ A9 18 A10 A10 4 19 A11 FIRQ A11 36 20 A12 MRDY A12 33 21 A13 DMA/B A13 22 A14 A14 23 A15 A15 31 D0 D0 30 D1 D1 29 D2 D2 28 D3 D3 Microprocesseur 27 D4 D4 26 D5 D5 25 D6 D6 24 D7 D7 34 E 35 Q 6 BA 5 BS 32 R/W 6809 Instruction : Mécanisme d’exécution 3ème étape L’instruction est exécutée avec positionnement des bus adresses, données et signaux de commande, le PC contient alors l’adresse de la prochaine instruction à exécuter .

Les modes d’adressages n°1 Inhérent : un seul octet, le code opération Exemple : NOP Immédiat : code opération Adresse de L’Eprom ex:C007 Contenu mémoire programme Exemple : LDA #$C9 Opérande Adresse suivante Mémoire 96 Instruction 42 Accumulateur A 7F LDA < $42 7F D342 Registre DP D3 Direct : Exemple : LDA <$42

Les modes d’adressages n°2 Etendu : code opération Adresse de L’Eprom ex:C007 Contenu mémoire programme Contient les poids forts de l’adresse de l’opérande: C9 Contient les poids faibles de l’adresse de l’opérande: 08 Exemple : LDA $C908 Opérande Adresse $C908 Cette adresse peut être dans n’importe quel circuit périphériques, l’adressage étendu permet de travailler sur toute la plae d’adressage du microprocesseur

PC $2001 PC $2003 X $D230 X $D230 ACCU A XX ACCU A $45 Mémoire programme Mémoire programme $2000 $2000 $2001 $A6 ($D230) $2001 $A6 $2002 05 =05 +PC $2002 05 $2003 PC = $D235 $2003 Mémoire des données Mémoire des données $D235 $D235 $45 $D236 $D236 $47 Les modes d’adressages n°3 Indexé : Exemple : LDA ,X +

Programme principal Sous programme Appel SPG Appel SPG Retour Les sous programmes Un sous programme est une partie répétitive de programme qui peut être appelée plusieurs fois dans le programme principal

Mécanisme d’appel à sous programme Contenu de la pile Temps 1Temps 2Temps 3Temps 4 $103$103$103 $303 Programme principal $100 Appel SPG1 $103 retour SPG1 1 SPG1 $280 SPG2 $300 Appel SPG2 2 $900 $303 retour SPG2 4 retour3 retour

Les interruptions But : interrompre le déroulement du programme pour traiter par le déroulement d’un programme d’interruption spécifique une tâche devenant prioritaire Le vecteur d’interruption est l’adresse fixée par le constructeur dont le contenu sera chargé dans le PC lors du déclenchement de l’interruption, ce contenu doit être l’adresse de début du programme d’interruption Mémoire Microprocesseur BUS E/S E/S IRQ IRQ IRQ Ligne d’interruption sur le bus de commande

Le décodage d’adresse Tous les périphériques étant reliés sur le même bus de données, lorsque le microprocesseur accède en lecture sur l’un d’eux, un conflit de bus peut se produire

Décodeur, une seule sortie à 0 à la fois A0 10 11 D0 A0 O0 A1 9 12 D1 A1 O1 A2 8 13 D2 Sorties actives pour A15=A14=A13=1 A2 O2 A3 7 15 D3 U? A3 O3 A4 6 16 D4 BIN/OCT A4 O4 1 15 A5 5 17 D5 A13 1 0 A5 O5 2 14 A6 4 18 D6 A14 CS2/ 2 1 A6 O6 3 13 A7 3 19 D7 A15 4 2 A7 O7 12 A8 25 3 A8 11 A9 24 & 4 A9 6 10 A10 21 5 A10 4 9 A11 23 Mémoire EN 6 A11 5 7 A12 2 CS1/ EPROM 7 A12 Mémoire Programme 20 74LS138 CS1/ CE 22 2764 OE 27 PGM 1 VPP U? 39 8 A0 8 9 U? X1 A0 A0 D0 9 A1 7 10 A1 A1 D1 10 A2 6 11 A2 A2 D2 38 11 A3 5 13 EX2 A3 A3 D3 12 A4 4 14 A4 A4 D4 37 13 A5 3 15 RESET A5 A5 D5 2 14 A6 2 16 NMI A6 A6 D6 15 A7 1 17 A7 A7 D7 40 16 A8 23 HALT A8 A8 3 17 A9 22 IRQ A9 A9 18 A10 19 A10 A10 4 19 A11 FIRQ A11 36 20 A12 18 CS2/ MRDY A12 CE 33 21 A13 20 DMA/B A13 OE 22 A14 21 A14 WE 23 A15 A15 6116 31 D0 D0 30 D1 D1 29 D2 D2 28 D3 D3 Microprocesseur 27 D4 D4 26 D5 D5 25 D6 D6 24 D7 D7 34 E 35 Q 6 BA 5 BS 32 R/W 6809 Réalisation pratique du décodage U? Sorties à haute impédance (« déconnectées »)

O O R SCIN SCOUT O M M SCILLATEUR ÉMOIRE ÉMOIRE P D D ROGRAMME E ONNÉE C HIEN INT EEPROM M ROM RAM ICROPROCESSEUR DE G ARDE Ou EPROM B - - US DONNÉES CONTRÔLE ADRESSES I I NTERFACE NTERFACE TIMER C.A.N S S P ÉRIE ARALLÈLE 1 2 CLK OUT A B C IMER IMER IN S S S T T ORT ORT ORT P P P Le microcontrôleur : architecture interne ESET

Les registres de la partie microprocesseur 1ère partie Programme counter (13 bits) UAL 8bits Pile 8 niveaux (13 bits) Registre W (accumulateur 8 bits) Registre FSR (adressage indirect) Registre d’état (status register)

Les registres de la partie microprocesseur 2ème partie Registre d’instruction Timing génération (circuit d’horloge) Registre de contrôle et décodage de l’instruction Multiplexeur données et adresse

vers décodeur Al0 lignes Al0/ Al1 Al1/ vers décodeur Ac0 colonnes Ac0/ Ac1 Ac1/ Décodeur Lignes 1 parmi m PLAN MEMOIRE Matrice de points mémoire P.M(ij) m lignes p colonnes m fois p cellules BUS ADRESSES Circuit adresse ligne Circuit adresse colonne Logique de commande Décodeur colonnes 1 parmi p Bus donnée Circuits d’entrée Circuits de sortie Circuits de lecture / écriture Généralités sur les circuits mémoires n°1 Structure interne

Les différents types de mémoire Généralités sur les circuits mémoires n°2 R.A.M : ramdom access mémory Mémoire volatile ou l’on peut lire et écrire dans n’importe quelle case mémoire sans ordre précis R.O.M : read only mémory Mémoire non volatile , avec accès en lecture uniquement et programmée par le constructeur de façon définitive P.R.O.M : Programmable read only mémory Mémoire non volatile , avec accès en lecture uniquement et programmée par l’utilisateur de façon définitive E.P.R.O.M : Erasable Programmable read only mémory Mémoire non volatile , avec accès en lecture uniquement , programmée par l’utilisateur, elle peut être effacée par rayonnement ultra violet et reprogrammée uncertain nombre de fois(quelques centaines) par un matériel spécifique E.E.P.R.O.M : Electrical erasable Programmable read only mémory Mémoire non volatile , avec accès en lecture uniquement , programmée par l’utilisateur, elle peut être effacée électriquement et reprogrammée un certain nombre de fois. (106) sans matériel spécifique et à partir de son alimentation (c’est presque une RAM non volatile)

Adresse valide Temps d’accès Donnée valide MEMOIRE Bus données Bus adresses t Généralités sur les circuits mémoires n°3 Lescaractéristiques essentielles d’une mémoire sont: - le temps d’accès qui est le temps entre l’instant où l’adresse est positionnée sur le bus d’adresse et l’instant où la donnée est disponible en sortie

Généralités sur les circuits mémoires n°3 bis - la capacité et le format des données Capacité = 2n mots où n est le nombre de fils du bus adresse Format du mot = nombre de fils du bus de données nombre de bit = Format du mot x 2n

Les périphériques du microcontrôleur: la mémoire programme De type Flash EEPROM Flash : accès rapide en écriture, la programmation est faite directement sur la carte d’émulation : programmation « in situ » Organisation: mémory map ou plan mémoire Accès : utilise des bus spécifiques séparés de la mémoire des données

Bank 0 Bank 1 Bank 2 Bank 3 Les périphériques du microcontrôleur: la mémoire des données Scindée en deux parties: une RAM et une EEPROM 0h 7Fh Data EEPROM 256 octets 80h FFh 100h 17Fh 180h 1FFh 368 octets

Organisée en «banks» elle contient les registres de gestion des circuits périphériques et les registres spécifiques La RAM data Accès à chaque bank par les bits RP0 et RP1 du registre STATUS

Les périphériques du microcontrôleur: les ports d’entrée/sortie Certaines lignes de port en plus de pouvoir être configurées en entrée ou en sortie , ont la particularité de pouvoir remplir d’autres fonctions comme sortie PWM, ligne usart, ligne I2C, lignes SPI…

Les registres de configuration du port A Le port A: configuration Exemple de programme d’initialisation

Les registres de configuration du port B Le port B: configuration et fonctions Les fonctions de chaque ligne

Les registres de configuration du port C Le port C: configuration et fonctions Les fonctions de chaque ligne

Les registres de configuration du port D Le port D: configuration et fonctions Les fonctions de chaque ligne

Les registres de configuration du port E Le port E: configuration et fonctions Les fonctions de chaque ligne

le convertisseur analogique numérique: généralités et définitions Rôle : convertir une tension analogique en une combinaison numérique sur n bits / format N bits Principe et généralité : CONVERTISSEUR ANALOGIQUE NUMERIQUE (C.A.N.) Les tensions de référence fixant la dynamique du signal d’entrée à convertir sont des données constructeur (Vref+ et Vref-) La valeur de quantification ou « QUANTUM » est déterminé par le nombre n de bits du convertisseur. q= (Vref+ - Vref-)1/2n

le convertisseur analogique numérique du microcontrôleur PIC16F877: structure

le convertisseur analogique numérique du microcontrôleur PIC16F877: configuration ,sélection de l’entrée