Test Bench

Test Bench

E N D

Presentation Transcript

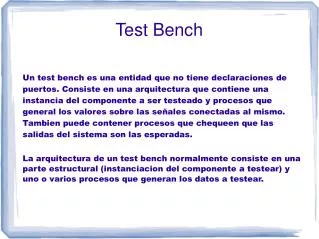

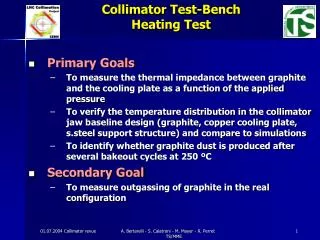

Un test bench es una entidad que no tiene declaraciones de puertos. Consiste en una arquitectura que contiene una instancia del componente a ser testeado y procesos que general los valores sobre las señales conectadas al mismo. Tambien puede contener procesos que chequeen que las salidas del sistema son las esperadas. La arquitectura de un test bench normalmente consiste en una parte estructural (instanciacion del componente a testear) y uno o varios procesos que generan los datos a testear. Test Bench

Estructura ENTITY test_bench IS END test_bench; ARCHITECTURE s OF test_bench IS COMPONENT clock PORT( clk: OUT std_logic ); END COMPONENT; COMPONENT wm PORT( clk, start, lid, pause: IN std_logic; ……); END COMPONENT; SIGNAL clk, start, lid, pause : std_logic_vector; BEGIN c : clock PORT MAP( clk => clk ); f : wm PORT MAP( clk => clk, start => start, lid => lid, … ); p : PROCESS BEGIN … END PROCESS; END ARCHITECTURE s;

entity reg4 is port ( d0, d1, d2, d3, en, clk : in bit; q0, q1, q2, q3 : out bit ); end entity reg4; architecture behav of reg4 is begin storage : process is variable stored_d0, stored_d1, stored_d2, stored_d3 : bit; begin wait until clk; if en then stored_d0 := d0; stored_d1 := d1; stored_d2 := d2; stored_d3 := d3; end if; q0 <= stored_d0; q1 <= stored_d1; q2 <= stored_d2; q3 <= stored_d3; end process storage; end architecture behav; Ejemplo de Test Bench

entity test_bench is end entity test_bench; architecture test_reg4 of test_bench is signal d0, d1, d2, d3, en, clk, q0, q1, q2, q3 : bit; begin dut : entity work.reg4(behav) port map ( d0, d1, d2, d3, en, clk, q0, q1, q2, q3 ); stimulus : process is begin d0 <= '1'; d1 <= '1'; d2 <= '1'; d3 <= '1'; en <= '0'; clk <= '0'; wait for 20 ns; en <= '1'; wait for 20 ns; clk <= '1'; wait for 20 ns; d0 <= '0'; d1 <= '0'; d2 <= '0'; d3 <= '0'; wait for 20 ns; en <= '0'; wait for 20 ns; ... wait; end process stimulus; end architecture test_reg4; Ejemplo de Test Bench

Waveform assignament: start <= ‘0’, ‘1’ after 1 sec, ‘0’ after 50 ms Loops dentro de procesos: process begin for j in 0 to 9 loop start<='0'; WAIT for 1 sec; start<=s(j); --tenemos una tabla con los valores cargados WAIT for 1 sec; --chequeo los resultados end loop; end process; Generacion de clock Driving signals al testbench

El tipo file en VHDL se utiliza para representar archivos. file nombre logico : nombre tipo [ open modo ] is ”archivo.ext” el modo puede ser write mode, read mode o append mode. Se utilizan las siguientes librerias: Textio: es una libreria para manejar textos. La entrada/salida de texto se realiza a traves de una variable tipo line. txt_util Escribiendo a archivos

PreDefined Files Input : Text is in "Std_Input"; -- usually mapped to keyboard Output : Text is out "Std_Output"; --usually mapped to console TextIO Type Text is file of String; Type Line is access String; Type Side is ( Right, Left ); Subtype Width is Natural;

procedure ReadLine ( F : in Text; L : out Line ); procedure Read ( L : inout; Value : out; |Good : out Boolean| ); Read is an Overloaded Procedure Where Value May be of Type: + Bit, Bit_Vector + Boolean + Character + Integer + Real + String + Time Read Procedures

procedure WriteLine ( F : out Text; L : out Line ); procedure Write ( L : inout;.. Write is an Overloaded Procedure Where Value May be of Type: + Bit, Bit_Vector + Boolean + Character + Integer + Real + String + Time Write Procedures

procedure file_open ( status : out file_open_status, file f : file_type, external_name : in string , open_kind : in file_open_kind := read_mode ) ; type file_open_status is ( open_ok, status_error, name_error, mode_error ) ; file_open_status open_ok File Opened Successfully status_error File Previously Opened name_error read_mode, append_mode - File Does Not Exist write_mode - Can Not Create File file_name mode_error File Exists But Can NotOpened in Specific Mode File I/O Status

file p_file : text open read_mode is "C:\CLASS\ALU.PAT" ; Begin Process Variable l : Line; Variable b : Bit; ... Begin While Not Endfile( f ) Loop Readline ( p_file, l ); Read ( l, b ); ... End Loop; End Process; End Arc; Ejemplo de lectura

file p_file : text open write_mode is "C:\CLASS\ALU.PAT" ; Begin Process Variable l : Line; Variable r : Bit_vector ( 31 downto 0 ) ; ... Begin For i in r'range Loop Write ( l, r ( i ) ); ... Writeline ( p_file, l ). ; End Loop; End Process; End Arc; Ejemplo de Escritura

use textio.all; architecture behavior of check is begin process (x) variable s : line; variable cnt : integer:=0; begin if (x='1' and x'last_value='0') then cnt:=cnt+1; if (cnt>MAX_COUNT) then write(s,"Counter overflow - "); write(s,cnt); writeline(output,s); end if; end if; end process; end behavior; ejemplo

library ieee; use ieee.std_logic_1164.all; use std.textio.all; use work.txt_util.all; entity FILE_LOG is generic ( log_file: string := "res.log" ); port( CLK : in std_logic; RST : in std_logic; x1 : in std_logic; x2 : in std_logic_vector(7 downto 0) ); end FILE_LOG; Escribiendo a archivos

architecture log_to_file of FILE_LOG is file l_file: TEXT open write_mode is log_file; Begin while true loop write(l, str(x1)&" "& hstr(x2)& "h"); writeline(l_file, l); end loop; Escribiendo a archivos

library ieee; use ieee.std_logic_1164.all; use std.textio.all; package txt_util is -- prints a message to the screen procedure print(text: string); -- prints the message when active -- useful for debug switches procedure print(active: boolean; text: string); -- converts std_logic into a character function chr(sl: std_logic) return character; -- converts std_logic into a string (1 to 1) function str(sl: std_logic) return string; Libreria TXT_UTIL

-- converts std_logic_vector into a string (binary base) function str(slv: std_logic_vector) return string; -- converts boolean into a string function str(b: boolean) return string; -- converts an integer into a single character -- (can also be used for hex conversion and other bases) function chr(int: integer) return character; -- converts integer into string using specified base function str(int: integer; base: integer) return string; -- converts integer to string, using base 10 function str(int: integer) return string; -- convert std_logic_vector into a string in hex format function hstr(slv: std_logic_vector) return string;

-- functions to manipulate strings ----------------------------------- -- convert a character to upper case function to_upper(c: character) return character; -- convert a character to lower case function to_lower(c: character) return character; -- convert a string to upper case function to_upper(s: string) return string; -- convert a string to lower case function to_lower(s: string) return string;

-- functions to convert strings into other formats -------------------------------------------------- -- converts a character into std_logic function to_std_logic(c: character) return std_logic; -- converts a string into std_logic_vector function to_std_logic_vector(s: string) return std_logic_vector; -- file I/O ----------- -- read variable length string from input file procedure str_read(file in_file: TEXT; res_string: out string); -- print string to a file and start new line procedure print(file out_file: TEXT; new_string: in string); -- print character to a file and start new line procedure print(file out_file: TEXT; char: in character); end txt_util;