Structural Description and Test Bench

Structural Description and Test Bench. Structural Description Positional association Named association “open” connection 3-bit up-down counter (Bhasker p. 135) Test Bench AND-gate example A typical structure Accumulator example Read Bhasker pp. 247-251 on “Factorial Circuit” test bench.

Structural Description and Test Bench

E N D

Presentation Transcript

Structural Description and Test Bench • Structural Description • Positional association • Named association • “open” connection • 3-bit up-down counter (Bhasker p. 135) • Test Bench • AND-gate example • A typical structure • Accumulator example • Read • Bhasker pp. 247-251 on “Factorial Circuit” test bench

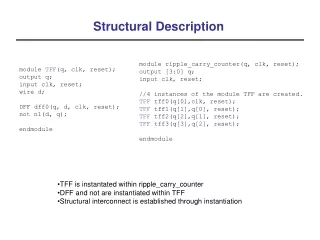

Structural Description • Positional Association Component NAND2 Port(A, B: in Std_logic, z: out std_logic); End component; -- In the architecture body N1: NAND2 port map(s1, s2, s3); • Named Association N1: NAND2 port map(B=>s2,A=>s1,z=>s3); • Key word “open” e.g., port B is left unconnected, however, we must specify an initial value in the component declaration Component NAND2 Port(A, B: in Std_logic := ‘1’, z: out std_logic); End component; -- In the architecture body N1: NAND2 port map(s1, open, s3); • 3-bit up-down counter example

Test Bench • Automating a Test Procedure using state machine • AND-gate test bench example -- 2-input AND gate library ieee; use ieee.std_logic_1164.all; entity and_gate is port(a, b: in std_logic; z: out std_logic); end and_gate; architecture dataflow of and_gate is begin z <= a and b; end dataflow;

library ieee; use ieee.std_logic_1164.all; entity testbench is end testbench; architecture behav of testbench is component and_gate port(a, b: in std_logic; z: out std_logic); end component; signal a, b, z : std_logic; signal ck : std_logic := '0'; signal test_a : std_logic_vector(0 to 3):= "0101"; signal test_b : std_logic_vector(0 to 3):= "0011"; type state_type is (load_test, check_result, done); signal next_state : state_type; begin ck <= not ck after 50 ns; dut: and_gate port map(a, b, z);

process(ck) variable count: integer := 0; begin if ck ='1' then case next_state is when load_test => a <= test_a(count);b <= test_b(count); next_state <= check_result; when check_result => assert z = (a and b) report "incorrect result" severity ERROR; count := count + 1; if count = 4 then next_state <= done; else next_state <= load_test; end if; when done => report "Test completed successfully"; end case; end if; end process; end behav;

Accumulator Example -- ECE-C302 Digital System Projects. -- Author: Dr. Nagvajara. -- Accumulator Example. -- synopsis: device accumulates integer, active-low. -- enable and clear, synchronous clear. ---------------------------------------------------- library ieee; use ieee.std_logic_1164.all; entity acc is. port( x : in integer; z : out integer; en, clr, CK :in std_logic); end acc;

architecture behav of acc is begin process(ck) variable temp : integer := 0; -- internal state begin if ck='1' and clr='0' and en='0' then temp := 0; elsif ck='1' and clr='1' and en='0' then temp := temp + x; else null; end if; z <= temp; end process; end behav;

-- TEST BENCH library ieee; use ieee.std_logic_1164.all; entity acc_test_bench is constant no_of_integers : natural := 5; end acc_test_bench; architecture behav of acc_test_bench is -- internal signal type controllers_state is (clear_accumulator,apply_number,wait_for_result, check_result); signal next_state : controllers_state; type set_of_number is array (natural range <>) of integer; signal number_set:set_of_number(0 to no_of_integers-1) := (10,10,10,10,10); signal x, z : integer; signal ref : integer := 50; signal enable,clear : std_logic; signal ck : std_logic := '0';

-- circuit under test component acc port (x : in integer; z : out integer; en, clr, CK : in std_logic); end component; begin -- clock process ck <= not ck after 50 ns; -- wire the circuit-under-test CUT: acc port map (x, z, enable, clear, CK); -- Test procedure process(CK) variable count : integer; begin if CK = '1' then case next_state is when clear_accumulator => enable <= '0'; clear <= '0'; count := 0; next_state <= apply_number;

when apply_number => clear <= '1'; x <= number_set(count); count := count + 1; if count < no_of_integers then next_state <= apply_number; else next_state <= wait_for_result; end if; when wait_for_result => enable <= '1'; next_state <= check_result; when check_result => if ref = z then assert false report "test completed successfully"; else assert false report "Result Incorrect"; end if; end case; end if; end process; End behav;