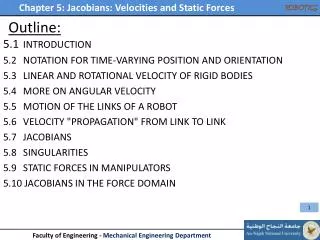

Outline

E N D

Presentation Transcript

60-GHz Direct-Conversion Transceiver on 130-nm CMOS with Integrated Digital Control InterfaceB. N. Wicks, C. M. Ta, F. Zhang, P. Nadagouda, B. Yang, Z. Liu, Y. Mo, K. Wang, T. Walsh, G. Felic, R. J. Evans, I. Mareels, and E. SkafidasNational ICT Australia (NICTA)Department of Electrical and Electronic Engineering The University of Melbourne

Outline • Introduction • Transceiver architecture • Experimental results • Conclusions and future works EuMIC 2009, Rome, Italy

Introduction • High data-rate applications • Peer-to-peer between portable devices: > 3 Gbps • PC connectivity for portable devices • HDMI cable replacement: up to 10 Gbps • 60-GHz wireless communications • Unlicensed band • 7 GHz of bandwidth • Low-cost semiconductor technology • CMOS EuMIC 2009, Rome, Italy

Transceiver architecture • 130-nm RF-CMOS • 5 mm × 5 mm • Direct-conversion architecture EuMIC 2009, Rome, Italy

Digital Control Interface (DCI) • Advanced CMOS technology • Shorter channel-length, lower power supply voltage, faster, more power efficient circuits • Analog/RF circuits become more sensitive to PVT variation • Digital techniques to compensate PVT effect EuMIC 2009, Rome, Italy

Performance - Transmitter • Power consumption: 515 mW • Output power: ~6.5 dBm EuMIC 2009, Rome, Italy

Performance - Receiver • Power consumption: 54 mW • Noise figure: 11 dB • iIP3: -13.7 dBm • Maximum conversion gain: 8.1 dB EuMIC 2009, Rome, Italy

Demonstration FPGA board EuMIC 2009, Rome, Italy

Conclusions • Integrated 60-GHz transceiver • 130-nm CMOS • Digital control interface • Demonstration EuMIC 2009, Rome, Italy

Future works • 65-nm CMOS • Phased-array Tx and Rx • Wire-bond and flip-chip • RF-ESD EuMIC 2009, Rome, Italy

60-GHz Direct-Conversion Transceiver on 130-nm CMOS with Integrated Digital Control InterfaceB. N. Wicks, C. M. Ta, F. Zhang, P. Nadagouda, B. Yang, Z. Liu, Y. Mo, K. Wang, T. Walsh, G. Felic, R. J. Evans, I. Mareels, and E. SkafidasNational ICT Australia (NICTA)Department of Electrical and Electronic Engineering The University of Melbourne