Efficient Escape Routing

380 likes | 544 Views

Efficient Escape Routing. Rui Shi, Chung-Kuan Cheng University of California, San Diego. Our Research Works. Escape routing bottleneck analysis Efficient escape routing for square array central triangular method two sided method sierra method

Efficient Escape Routing

E N D

Presentation Transcript

Efficient Escape Routing Rui Shi, Chung-Kuan Cheng University of California, San Diego

Our Research Works • Escape routing bottleneck analysis • Efficient escape routing for square array • central triangular method • two sided method • sierra method • Efficient escape routing for hexagonal array

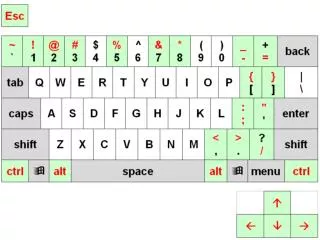

Problem Definition • Problem: Escape the I/Os in an area array to the outside. • Area Array: • Full populated array: all I/Os are taken into consideration for analysis • Escape Routing: • Assume blind vias are used • Objective: • Maintain high density of I/Os in array • Reduce the number of routing layers used for escaping • Applications: • Interconnection from chip to package • Interconnection from package to board

Escape routing bottleneck analysis • Maximum flow formulation • Build routing graph for the area array • Solve maximum flow problem on the routing graph • Define bottleneck edge as the edge whose flow is equal to its capacity • Define bottleneck contour as the profile formed by all the bottleneck edges • The maximum flow solution is a upper bound

Escape routing bottleneck analysis (Cont.) • Escape bottleneck experimental results • Parameters used: • the pad pitch = 150m • the pad diameter = 75m • the line width = 20m • the spacing = 20m • the array size = 40 • Six square area array patterns

Escape routing bottleneck analysis (Cont.) Maximum flow value = 370.50 Maximum flow value = 446.23

Escape routing bottleneck analysis (Cont.) Maximum flow value = 438.93 Maximum flow value = 447.26

Escape routing bottleneck analysis (Cont.) Maximum flow value = 271.62 Maximum flow value = 428.59

Escape routing bottleneck analysis (Cont.) • Conclusions: • The bottleneck contour always follows the outline of the array • The array outline with larger capacity has the potential to decrease the number of routing layers • I/Os escaped in previous layers will form the outline for the following layers

Efficient escape routing for square array • Central triangular method • Escape I/Os from the center of the outside row and expands the indent with a single triangular outline. In this method, the outline capacity is increased continuously layer by layer.

Efficient escape routing for square array • Two sided method • Escape I/Os from inside and outside simultaneously. The outline will shrink slowly and follow zigzag shape.

Efficient escape routing for square array • Sierra method • Escape I/Os from the center of the outside row and expands the indent with a sierra triangular outline. Break out I/Os in every layer as many as possible.

Experimental Results 40 x 40

Experimental Results 20 x 20

Efficient escape routing for hexagonal array • Using same area and same I/O pitch, the hexagonal array can hole more I/Os and have larger I/Os density • Using same area and holding similar number of I/Os, the hexagonal array can separate the I/Os loosely and have larger I/O pitch

Efficient escape routing for hexagonal array • Column-by-Column Horizontal Escape Routing

Efficient escape routing for hexagonal array • As long as the condition is satisfied, I/Os in the hexagonal array can be escaped within the same number of routing layers as square grid array unit: m (ITRS)

Efficient escape routing for hexagonal array • Two-sided Horizontal/Vertical Escape Routing

Efficient escape routing for hexagonal array • Multi-direction Hybrid Channel Escape Routing

References • M. Horiuchi, etc., “Escape routing design to reduce the number of layers in area array packaging”, Advanced Packaging, IEEE Trans., 2000 • A. Titus, etc., “Innovative Circuit Board Level Routing Designs for BGA Packages”, Advanced Packaging, IEEE Trans., 2004 • R. Shi, etc., “Layer Count Reduction for Area Array Escape Routing”, IMAPS International Conference and Exhibition on Device Packaging, 2005 • R. Shi, etc., “Efficient Escape Routing for Hexagonal Array of High Density I/Os”, DAC, 2006 • R. Wang, etc., “Layer Minimization of Escape Routing in Area Array Packaging”, ICCAD, 2006