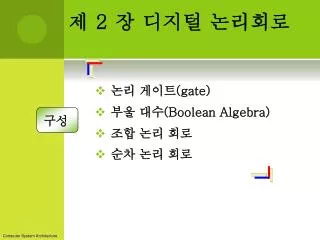

제 2 장 디지털 논리회로

구성. 제 2 장 디지털 논리회로. 논리 게이트( gate) 부울 대수( Boolean Algebra) 조합 논리 회로 순차 논리 회로. 논리 게이트. 논리회로는 서로 다른 두 가지 값 (0,1)을 다루는 회로 동작 특성 : 부울 대수로 표현 디지털 컴퓨터에서 이진 정보 : ADC(Analog to Digital Conversion) Physical Quantity Signal Binary Information 예 : V, A, F, 거리 Discrete Value.

제 2 장 디지털 논리회로

E N D

Presentation Transcript

구성 제 2 장 디지털 논리회로 • 논리 게이트(gate) • 부울 대수(Boolean Algebra) • 조합 논리 회로 • 순차 논리 회로

논리 게이트 • 논리회로는 서로 다른 두 가지 값 (0,1)을 다루는 회로 • 동작 특성 : 부울 대수로 표현 • 디지털 컴퓨터에서 이진 정보 : ADC(Analog to Digital Conversion) • Physical Quantity Signal Binary Information 예 : V, A, F, 거리Discrete Value 0 : 0.5V 1 : 3V~5V

논리 게이트 • 게이트 • 이진 정보를 처리하는 가장 기초적인 논리회로 소자 • 각 게이트의 동작 : 부울 대수/함수 • 게이트의 입출력 관계 : 진리표(Truth table) • George Boole • 출생 : 영국의 링컨에서 출생 • 사고법칙에 대한 고찰(Investigation of the Laws of Thought)이라는 제목으로 책을 만들었는데, 여기에서 형식논리와 오늘날 부울 대수라 알려진 집합의 대수인 새로운 대수학을 확립. • 부울 대수는 전기 스위치 회로이론 등과 같은 수많은 분야에 응용되고 있다.1859년에 부울은 <미분방정식론, Treatise on Differential Equations>, 1860년에는 <차분법론, the Calculus of finite differenes>을 발표

논리 게이트 • 표 2-1 Digital Logic Gates • AND, OR, INVERTER, BUFFER, NAND, NOR, XOR, XNOR F = A’ F = A·B F = A + B OR gate AND gate NOT gate F = A F = (A·B)’ F = (A + B)’ NOR gate NAND gate Buffer gate F = A B F = A B XNOR gate XOR gate

논리 게이트 • [문제 2-1] 두 개의 입력(two input)을 가지는 게이트에서 입력 신호 A, B의 조합에 따른 출력 타이밍도(timing diagram)를 그려라.

유니버설 게이트 • NAND와 NOR 게이트 : 표준 논리 게이트 • 모든 부울 함수 : NAND와 NOR 게이트로서 쉽게 구현 • NOT 게이트 • AND 게이트 OR 게이트 Fig. 2-2

WIRED-LOGIC • NAND와 NOR 게이트 : 둘 이상의 게이트 출력을 선(Wire)으로 연결하면 AND/OR 논리를 수행 Wired-logic • 개방 콜렉터형 NAND 게이트 Fig. 2-3 Fig. 2-4 • ECL NOR 게이트

부울 대수(BOOLEAN ALGEBRA) • 부울대수(Boolean Algebra) • 이진 변수(binary variable) + 논리 동작(logic operation) 을 취급하는 대수 (A, B, x, y 등) (AND, OR, NOT…) • 부울대수의 기본 연산 • AND, OR, NOT 연산 • 부울대수의 사용 목적 : 디지털 회로의 설계와 해석을 용이

A B C F 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1 부울 대수(BOOLEAN ALGEBRA) • 부울대수를 이용하면 • ① 변수 사이의 진리표 관계를 대수형식으로 표시하기가 용이 • ② 논리도의 입출력 관계를 대수형식으로 표시하기가 용이 • ③ 동일 기능을 가진 더 간단한 회로(논리식의 간소화)를 설계하는 것이 용이 • Truth Table : Fig. 2-5Relationship between a function and variable • Logic Diagram : Fig. 2-5 대수적 표현논리도(Logic Diagram)(gates로 표현) 2n Combination Variable n = 3

부울 대수(BOOLEAN ALGEBRA) p60~p65 참조 - Operation with 0 and 1: x + 0 = x , x + 1 = 1 , x • 1 = x , x • 0 = 0 - Idempotent Law: x + x =x , x • x = x - Complementary Law: x + x' = 1 , x • x' = 0 - Commutative Law: x + y = y + x , x • y = y • x - Associative Law: x + (y + z) = (x + y) + z , x • ( y • z) = (x • y) • z - Distributive Law: x • ( y+ x) = (x • y) + (x • z) , x + (y • z) = (x + y) • (x + z) - DeMorgan's Law: (x + y)' = x' • y’ , (x • y )’ = x’ + y’ n개의 변수로 확장한 일반식 (x1 + x2 + x3 + … xn)' = x1' • x2' • x3' • … xn’ (x1 • x2 • x3 • … xn) ' = x1' + x2' + x3' + … xn’ • 부울대수 법칙 : Table. 2-5 참조

드모르강 정리 • DeMorgan's Law: (x + y)' = x' • y’ , (x • y )’ = x’ + y’ • 연산자와 변수로 구성된 임의의 함수가 있을 때 이 함수의 전체 부정은 연산자 +는 ·로, ·는 +로 바꾸고(+ ↔ ·) 함수에 포함된 변수는 긍정은 부정으로 부정은 긍정으로(A' ↔ A)으로 바꾸어 각각의 변수에 대한 부정을 취하는 것과 결과가 같음을 나타내는 법칙으로 NAND와 NOR를 취급하는데 유용 • 드모르강의 정리 • graphic symbols for NOR gate (a) OR-invert (b) invert-AND x y z x y z = (x+y+z)’ x’y’z’

graphic symbols for NAND gate (a) AND-invert (b) invert-OR x y z x y z = (xyz)’ (x’+y’+z’) • [표 2-5]의 부울대수 기본관계식의 적용 예 Fig. 2-6 F=AB'C+AB'C'+A'C

[표 2-5]의 1-5와 2-2에 의해 F=AB'C+AB'C'+A'C =AB'(C+C')+A'C =AB'+A'C • [표 2-5]의 부울대수 기본관계식의 적용 예 Fig. 2-7 F=AB'+A'C 간소화된 함수식에 의한 회로로서 다섯 개의 게이트들만을 이용하여 [그림 2-6]과 동일한 결과

수식의 보수 • 어떤 함수 F의 보수는 F'이며, 드모르강 정리를 이용하여 얻을 수 있다. 드모르강 정리는 부울 함수식에서 모든 OR연산은 AND로, 모든 AND 연산은 OR로 바꾸어 주고, 함수 내의 각 변수를 보수화하면 된다. • 예를 들어 다음과 같은 부울 함수식의 보수를 만들어 보자. • F = AC + C'D + B'D'의 보수는 F'= (A'+C')(C+D')(B+D) 이 된다. • 수식의 보수

부울 함수 F1 = ABC' F2 = A + B'C F3 = AB'C+AB'C'+A'C F4 = AB' + A'C • 부울함수(Boolean Function) : variable + operation(AND, OR, NOT)+ 괄호 + 등호 • 예 • 위 부울함수의 입출력 관계 진리표 n개의 2진 변수 2n개의 조합 • F1은 A=1, B=1, C=0일 때만 출력 F1 = 1 • 마찬가지로 함수 F2, F3, F4도 같은 방법 적용

부울 함수 Tab. 2-6 • 부울 함수 F1 , F2 , F3 , F4에 대한 진리표 F1 = ABC', F2=A+B'C, F3 = AB'C+AB'C'+A'C, F4 = AB'+A'C에 대한 진리표 진리표에서 F3과 F4는 동일한 함수값, 같은 부울 함수에 대해 서로 다른 대수적 표현이 가능하다는 것을 의미, 이 두 함수는 같다고 말한다. 함수 F4는 함수 F3을 간소화 한 것이다.

부울 함수 • 부울 함수 논리도(Logic Diagram) (a) F1 = ABC' (b) F2=A+B'C (c) F3 = AB'C+AB'C'+A'C (d) F4 = AB'+A'C • 함수 F4가 함수 F3보다 더 경제적

부울 함수의 표준형(standard form) • 2 variables example • 최대항(Minterm)과 최소항(Maxterm) • 최소항(Minterm) : n variables product ( x=1, x’=0) • 최대항(Maxterm) : n variables sum (x=0, x’=1) m0 + m1 + m2 + m3 M0 M1 M2 M3

최소항의 합(sum of product) • 부울 함수는 주어진 진리표를 보고 대수적으로 표시 최소항의 합 최대항의 곱 • 최소항의 합 진리표에서 출력값이 1이 되는 최소항을 구하고 이 최소항에 대해 모두 OR연산을 취함 • F1 = x'y'z + xy'z' + xy'z + xyz' = m1 + m4 + m5 + m6 =∑(1, 4, 5, 6) =M0· M2· M3· M7=∏(0, 2, 3, 7) (Complement = M0 M2 M3 M7)

최대항의 곱(product of sum) • 부울 함수는 주어진 진리표를 보고 대수적으로 표시 최소항의 합 최대항의 곱 • 최대항의 곱 진리표에서 출력값이 0이 되는 최대항을 구하고 이들 최대항들에 대해 모두 AND연산을 취함 • F2 = (x+y+z')·(x'+y+z)·(x'+y+z')·(x'+y'+z)=M1· M4· M5· M6 =∏(1,4, 5, 6)

부울함수의 간소화 • 식에 포함된 문자와 항들의 개수를 줄여 간단한 형태로 유도하는 절차 논리 게이트를 이용한 설계가 간단하여 구현시 가격, 유지보수에 유리 (1) 정리와 가설을 이용한 간소화 방법 Tab. 2-5 F = AB' + B = B + A B' = (B + A)(B + B') = (B + A)·1 = B + A = A + B 1-7 적용 1-12 적용 1-5 적용 2-3 적용 1-7 적용

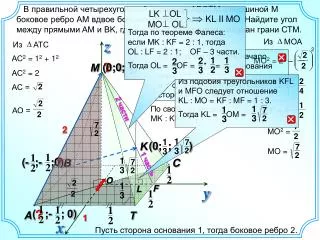

C B A B A C D 부울함수의 간소화 • 3 variables • 4 variables B (2) Map을 이용한 간소화 방법 • 2 variables A • 5 variables C B A D E F • 논리적으로 인접한 항이 포함되도록 2, 4, 8, 16개 그룹으로 묶으면 그만큼 지워지는 변수가 많아지므로 가능한 한 많은 수의 항을 묶어야 하며, 간소화된 항들은 최소항의 합형이나 최대항의 곱형으로 표현

y x 부울함수의 간소화 (1) 진리표 (2) (3) 인접 영역을 묶는다 • [예제] F= x + y’z 1 1 1 1 1 z F= x + y’z

부울함수의 간소화 • 인접 영역 • 인접 영역의 수 = 2n (1, 2, 4, 8, ….) • The squares at the extreme ends of the same horizontal row are to be considered adjacent • The same applies to the top and bottom squares of a column • The four corner squares of a map must be considered to be adjacent • Groups of combined adjacent squares may share one or more squares with one or more group

C C B B A A B B A A C C D D 부울함수의 간소화 • [예제] • F=C’ + AB’ • [예제] • F=AC’ + BC • [예제] • F=C’ + AB’ • Product-of-Sums Simplification F=B’D’ + B’C’ + A’C’D F’=AB + CD + BD’(square marked 0’s) (F’)’=(A’ + B’)(C’ + D’)(B’ + D) Sum of product Product of Sum

MAND/NOR 게이트로의 구현 B’ D’ C’ A’ D • NAND Implementation • Sum of Product : F=B’D’ + B’C’ + A’C’D • NOR Implementation • Product of Sum : F=(A’ + B’)(C’ + D’)(B’ + D) • 무관 조건(Don’t care conditions) • F(A,B,C)=(0, 2, 6), d(A,B,C)= (1, 3, 5) • F=A’ + BC’= (0, 1, 2, 3, 6) A’ B’ C’ D’ D’ B 1 1 X X A 1 X C

조합 논리 회로(Combinational Circuit) i f • 조합 논리 회로(Combinational Circuits) • 입력과 출력을 가진 논리 게이트(logic gates)의 집합으로 출력은 현재의 입력값에 의해 결정 • Fig. 2-12조합회로 블록도 • 해석(Analysis) • Logic circuits diagram Boolean function or Truth table • 설계(Design)(Analysis의 반대) • 1. 주어진 문제를 분석 • 2. 입출력 변수의 개수를 결정/입출력 변수에 기호 할당 • 3. 입출력 변수에 대한 진리표 작성(Truth table) • 4. 출력을 간소화된 부울 함수로 표현(Map 과 Boolean 대수 이용) • 5. 논리 회로를 작성(Logic circuit diagram) 0 0 i f Combinational Circuits (Logic Gates) 1 1 . . . . . . i f n m Experience

조합 논리 회로(Combinational Circuit) i f 0 0 i f Combinational Circuits (Logic Gates) 1 1 . . . . . . • 조합 논리 회로(Combinational Circuits) i f n m • 【문제2.6】위의 그림과 비교하면서 다음 문제를 생각해 봅시다. 그림 2-13에서 몇 개의 입력 조합이 나타나는가? 또 몇 개의 출력이 나오는가? Fig. 2-13

조합 논리 회로 해석 예 • 조합 회로의 해석은 주어진 논리 회로도로부터 부울 함수나 진리표 를 구하고 논리 회로의 동작을 해석 • 해석 과정 (1)논리 회로도에서 해석을 위해 필요한 입·출력 변수명을 결정한다. (2) n개의 입력 변수에 대한 2n개의 입력조합과 출력 변수에 대한 진리표를 작성하거나 각 게이트의 출력 부울 함수를 구한다. (3) 최종 출력 부울 함수를 구한 후 간소화한다. (4) 출력 부울 함수와 진리표를 통해 논리 회로의 동작을 해석한다.

조합 논리 회로 해석 예 Fig. 2-14 • 그림 2-14와 같은 조합 회로를 해석 • 3개의 입력변수와 1개의 출력변수 (1) 입력변수 : A, B, C출력변수 : F 해석을 위한 임시변수 : T1, T2, T3을 결정 (2) 입력변수에 대한 진리표를 작성 혹은 각 게이트의 출력을 구한다. T1 = AB', T2 = AB'C, T3 = A'B (3) 최종 출력 부울 함수를 구한다. F = T1 + T2 + T3 = AB' + AB'C + A'B F = AB' + A'B 간소화

조합 논리 회로 설계 예 반가산기(Half Adder : HA) 전가산기(Full Adder : FA) • 가산기( Adder) • 1비트의 두 2진수를 더하는 조합 논리 회로 • 반가산기 : 2 입력(A, B)과 2 출력(합 : S, 자리올림 : C) 전가산기 : 3 입력 (Carry considered)(A, B, C0)과 2 출력 (합 : S, 자리올림 : C1) • 진리표 • 반가산기 • 전가산기

조합 논리 회로 설계 예 • 4. 맵을 이용한 간소화 • 설계 예 : 전가산기(Full Adder)를 설계하시오. • 1. 문제 분석 • 2. 입출력 변수의 개수를 결정/ 변수를 할당 3 입력(A, B, C0), 2 출력(S: sum, C1: carry) • 3. 진리표 작성 S=AB’C0’ + A’B’C0 + ABC0 + A’BC0’ = C0’(AB’ + A’B) + C0(A’B’ + AB) = C0’(A B) + C0(A B)’ = a’b + ab’ (let a= C0, b=AB) = A B C0 C1 = AB’C0 + A’BC0 + AB =C0(AB’ + A’B) + AB = C0 (A B) + AB • 5. 논리 회로도 (AB)’=(AB’+A’B)’ =(A’+B)(A+B’) =A’A+A’B’+AB+BB’ =A’B’+AB

조합 논리 회로 설계 예 반감산기(Half Subtractor : HS) 전감가산기(Full Subtractor : FS) • 감산기( Subtractor) • 1비트의 두 2진수를 감산하는 조합 논리 회로 • 반감산기 : 2 입력(X, Y)과 2 출력(차 : D, 자리빌림 : B) 전감산기 : 3 입력(X, Y, B0)과 2 출력 (차 : D, 자리빌림 : B1) • 진리표 • 반감산기 • 전감산기

조합 논리 회로 설계 예 • 디코더(Decoder) • n비트의 2진 입력을 받아 2n개의 출력 중 하나를 활성화 • 활용 : 메모리 칩 선택 신호, 명령어 해독과 제어 장치 등에 사용 • n×2n디코더 : n개의 입력과 2n개의 출력 • 2 × 4 디코더를 설계 • 1. 입출력 변수의 개수를 결정/변수를 할당 2 입력 (A, B), 4 출력(D0, D1, D2, D3) • 2. 진리표를 작성 • 3. 맵을 이용한 간소화 • 4. 논리회로 작성 Fig. 2-21 2×4 디코더

조합 논리 회로 설계 예 • 디코더(Decoder) • 회로동작 제어를 위해 인에이블(enable) 입력 사용 • 예 : 그림 [2-22] • enable input = 0, 모든 출력 0 • enable input = 1, 정상 동작 Fig. 2-22 인에이블 입력을 가지는 3×8 디코더 블록도

조합 논리 회로 설계 예 • 디코더(Decoder)를 이용한 조합 논리 회로 설계 • n개의 입력변수들에 대한 2n개의 최송항 표현 • 이를 이용하여 임의의 조합 논리 회로 설계시 디코더를 사용 • 즉, 모든 부울함수는 최소항의 합형으로 표현 가능 디코더 최소항 표현, 합 OR게이트 이용 • n개의 입력과 m개의 출력을 가지는 임의의 조합 회로를 설계하려면 n × 2n디코더와 m개의 OR 게이트로 구현 가능 • 예 : 전가산기를 디코더로 설계(입력변수 3개, 출력변수 2개) S(A,B,C0) = ∑(1, 2, 4, 7) C1(A,B,C0) = ∑(3, 5, 6, 7) Fig. 2-23

조합 논리 회로 설계 예 • 인코더(Encoder) • 디코더의 반대 기능을 수행, OR 게이트로 구성 • 2n개의 입력과 n개의 출력 • 8진× 2진 인코더 설계 • 1. 입출력 변수의 개수를 결정/변수를 할당 8 입력 (D0, D1, D2, D3, D4, D5, D6, D7), 3 출력(A,B,C) • 2. 진리표를 작성 • 3. 진리표로부터 출력 부울 함수를 구하면 A = D4 + D5 + D6 + D7 B = D2 + D3 + D6 + D7 C = D1 + D3 + D5 + D7 • 4. 논리회로 작성

조합 논리 회로 설계 예 Fig. 2-24 8진-2진 인코더 • 입력 D0은 어떤 OR 게이트에도 연결되지 않았는데 이 경우에 2진 출력은 모두 0이 되어야 하기 때문이다. 회로에서 인코더의 입력은 단지 하나의 입력만이 1이 된다고 가정. 왜냐하면 이 회로에서 입력은 8개이므로 28=256가지의 입력 조합이 나타난다. 그러나 이들 중 단지 8개만이 의미 있는 입력이므로 다른 입력들은 전부 무관조건이 된다.

조합 논리 회로 설계 예 • 멀티플렉서(Multiplexer) • 여러개의 입력선 중의 한 선으로부터 정보를 받아들여 단일의 출력선 으로 정보를 출력하는 조합 논리 회로 • 특정 입력선의 선택은 선택선(Select line)에 의해 제어 • 2n개의 입력과 1개의 출력, n개의 선택선 • 4× 1 멀티플렉서 설계 • 1. 입출력 변수의 개수를 결정/변수를 할당 4 입력 (I0, I1, I2, I3), 1 출력(Y), 2 선택선(S0, S1) • 2. 함수표(진리표)를 작성 • OR게이트의 역할 : 선택된 입력과 출력을 연결시켜 주는 통로 Fig. 2-25(a) • 3. 논리회로 작성

조합 논리 회로 설계 예 • 4개의 2×1 멀티플렉서(Multiplexer) • Enable input = 0 , 정상 동작 • 선택선 S와 인에이블 입력선 E는 공통으로 인가 Fig. 2-25(a) (b) 함수표 (a) 블록도

조합 논리 회로 설계 예 Fig. 2-27 • 디멀티플렉서(DeMultiplexer) • 멀티플렉서의 역기능을 수행 • 하나의 입력선과 2n개의 출력선, n개의 선택선으로 구성 • 1×4 디멀티플렉서 (b) 함수표 (c) 블록도 (a) 회로도

조합 논리 회로 설계 예 Fig. 2-28(a) • 4. 논리 회로 작성 • 코드 변환 회로(2진/그레이 코드 변환기) • 그레이 코드 : 서로 이웃한 수끼리 1비트만 다르게 구성된 코드 • 3비트의 2진수를 그레이 코드로 변환하는 회로 설계 • 1. 입출력 변수의 개수를 결정/변수를 할당 3 입력 (a, b, c), 3 출력(x, y, z) • 2. 진리표를 작성 • 3. 맵을 이용한 간소화 : 출력 부울 함수 유도 x = a y = a'b + ab' z = b'c + bc'

조합 논리 회로 해석 예 ① 2진수의 최상위 비트는 그레이 코드의 최상위 비트가 된다. ② 최상위 비트부터 한 비트씩 오른쪽으로 진행하면서 이웃하는 2개의 2진수에 대한 XOR 연산을 수행하면 그 결과가 그레이 코드가 된다. ③ 마지막 코드가 얻어질 때까지 ②번을 반복한다. • 2진수/그레이 코드 변환 과정 • 그레이 코드/2진수 변환 과정 ① 그레이 코드의 최상위 비트는 2진수의 최상위 비트가 된다. ② 최상위 비트와 두 번째 비트를 XOR 연산하면 결과가 2진수가 된다. ③ 두 번째 2진수 비트와 세 번째 그레이 코드의 비트를 XOR 연산하면 결과가 2진수가 된다. ④ 마지막 코드가 얻어질 때까지 ③번을 반복한다.

조합 논리 회로 설계 예 • ROM을 이용한 조합 회로 설계 • 2.3.4에서 디코더를 이용한 조합회로 설계 • ROM = 디코더 + OR • 디코더의 출력들과 OR게이트의 입력들을 서로 연결 ROM을 프로그래밍 • n개의 입력선과 m개의 출력선으로 구성 • 2n개의 워드(word)와 워드당 m 비트로 구성 Fig. 2-34 ROM 블록도 • n개의 입력과 m개의 출력을 가지는 조합회로를 ROM을 이용하여 구현 2n x m ROM이 필요 • 예 F1(A, B) = ∑(1, 2, 3) F2(A, B) = ∑(1, 3)

조합 논리 회로 설계 예 • ROM을 이용한 조합 회로 설계 • 구현 : 2개의 입력과 2개의 출력을 가지는 ROM 필요 • ROM의 크기 4 x 2 Fig. 2-35 F1(A, B) = ∑(1, 2, 3) F2(A, B) = ∑(1, 3) 4 x 2 ROM으로 조합 회로 구현

순차 논리 회로(Sequential logic circuit) Combinational Circuit = Gate Sequential Circuit = Gate + F/F • 순차 논리 회로 • 조합 논리 회로 + 메모리 요소(플립플롭) • 출력 : 입력변수의 값과 현재상태[ Q(t)]의 값에 의해 결정 • 메모리요소 : 플립플롭(f/f) 한 비트의 이진 정보를 저장할 수 있는 이진 셀(cell) 정상 출력 Q(t)과 보수 출력 Q’(t) Fig. 2-36 순차회로 블록도 동기식(synchronous) 비동기식(asynchronous)

플립 플롭(Flip flop) Fig. 2-38 • 기본 플립 플롭 회로 • 2개의 NAND 게이트 혹은 NOR 게이트로 구성 • SR 래치(latch)

플립 플롭(Flip flop) Fig. 2-39 • SR(Set/Reset)플립플롭 논리도 기호 특성표 특성 방정식

플립 플롭(Flip flop) • D(Data)플립플롭 • “no change” condition이 없다 : Q(t+1)=D • 해결방법 : 1) Disable Clock 2) Feedback output into input Fig. 2-40 Fig. 2-41 • JK(Jack/King)플립플롭

플립 플롭(Flip flop) • T(Toggle)플립플롭 Fig. 2-42 논리도 특성표 기호 특성 방정식