Uvod

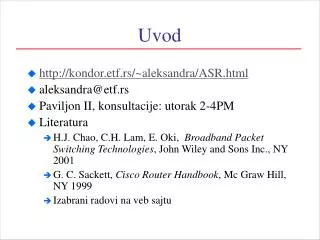

Uvod. http://kondor.etf.rs/~aleksandra/ASR.html aleksandra@etf.rs Paviljon II, konsultacije: utorak 2-4PM Literatura H.J. Chao, C.H. Lam, E. Oki, Broadband Packet Switching Technologies , John Wiley and Sons Inc., NY 2001 G. C. Sackett, Cisco Router Handbook , Mc Graw Hill, NY 1999

Uvod

E N D

Presentation Transcript

Uvod • http://kondor.etf.rs/~aleksandra/ASR.html • aleksandra@etf.rs • Paviljon II, konsultacije: utorak 2-4PM • Literatura • H.J. Chao, C.H. Lam, E. Oki, Broadband Packet Switching Technologies, John Wiley and Sons Inc., NY 2001 • G. C. Sackett, Cisco Router Handbook, Mc Graw Hill, NY 1999 • Izabrani radovi na veb sajtu

Ispit • Ispit se radi kroz projekat. • Studenti podeljeni u timove, dva/tri studenta u timu. • Projekat je modeliranje i analiza performansi paketskog sviča, odnosno rutera za zadate matrice saobraćaja. • Modeliranje u programskom jeziku C. • Pisani izveštaj treba da obuhvati kratak opis rutera, algoritma, opis matrica saobraćaja, i analizu performansi sviča. Nosi 50 poena. • Studenti pojedinačno usmeno prezentiraju projekat uz slajdove, i odgovaraju na dva teorijska pitanja. Usmena prezentacija projekta nosi 34 poena, odgovori 14 poena i poseta Iritelu 2 poena.

Raspored kursa • Nov. 6. - Uvod i Paketsko procesiranje. • Nov. 7. - Paketsko procesiranje: IP lukap. • Nov. 13. - Paketski svičevi sa izlaznim baferima i paketski svičevi sa zajedničkim baferom. • Nov. 20. - Paketski svičevi sa ulaznim baferima. • Okt. 27. - Implementacija funkcionalnosti paketskih svičeva u FPGA čipovima.Opis projekta i priprema za lab vežbe.

Raspored kursa • Dec. 4. -Birkoff-von-Neumanni multistepeni svičevi • Dec. 11. – Poseta Iritelu • Dec. 18., 25.– Lab vežbe

Svičevi ili komutatori • Svičevi (komutatori) • Sa komutacijom kola • Paketski svičevi • Svičevi sa komutacijom kola • Telefonske centrale • Transportni svičevi • Paketski svičevi su jezgro • Mostova • Rutera

Arhitektura Internet rutera i paketskih svičeva • Paketski procesor • Procesiranje sloja 2 • Lukap • Segmentacija i rekonstrukcija paketa • Paketski svič (komutator) • Centralni procesor • OSPF, RIP,BGP • MPLS • Protokoli zaštite

Terminologija • Paketski svič ili komutator je sastavni deo mosta ili Internet rutera. • Pošto most odnosno ruter najpre odrede svoj izlazni port na koji je okvir odnosno paket usmeren na osnovu MAC adrese okvira odnosno IP adrese paketa. • Zatim je okvir odnosno paket prosleđen kroz komutator. Komutator sadrži bafere. Kontroler komutatora određuje da li i kada će okviri odnosno paketi biti prosleđeni kroz komutator. • Vendori mostove zovu svičevima (na engleskom Ethernet switch obavlja i funkcije mosta).

Arhitektura Internet rutera ULAZNO IZLAZNI MODUL ULAZNO IZLAZNI MODUL ULAZNO IZLAZNI MODUL CENTRALNI PROCESOR GENERATOR TAKTA KOMUTATOR

LUKAP MEMORIJA PROCESOR FIZIČKOG SLOJA PROCESOR SLOJA LINKA MREŽNI PROCESOR BAFER BAFER MREŽNI PROCESOR PROCESOR SLOJA LINKA PROCESOR FIZIČKOG SLOJA Ulazno-izlazni modul-Paketski procesor SPI-4, (POS-PHY-4) SFI-4 SFI-4 SerDes Framer Interface SPI-4 System Packet Interface

Standardizovani interfejsi čipova • SFI-x (SerDes Framer Interface) i SPI-x (System Packet Interface) su OIF (Optical Internetworking Forum) standardi.x=3 za 2.4Gb/s, x=4 za 10Gb/s i x=5 za 40Gb/s brzinu portova • SFI-x je interfejs između SerDes čipa optičkog primopredajnika i procesora fizičkog sloja. Može povezati više čipovakoji izvršavaju protokole fizičkog sloja. Definiše format signala, i klokova, kao i proces kodovanja i sinhronizacije. • SPI-x je interfejs preko koga se prenose paketi promenljive dužine. Definiše format signala, i klokova, kao i kontrolu toka. Takođe razgraničava pakete i adresira kanale kojima paketi pripadaju.

Paketski procesor • SDH frejmer prilagodjava SDH signal transiverima na ploči, i procesira SDH zaglavlje • Procesor sloja linka izdvaja okvire i pakete, dekoduje signal i konvertuje signal u odgovarajući format • Mrežni procesor obrađuje IP zaglavlje, i vrši IP lukap, odnosno određuje izlazni port na osnovu IP adrese • Paketi, odnosno ćelije se čuvaju u baferima pre i/ili posle komutacije

Proizvođači • Vendori čipova su: Agere Systems, PMC Sierra, Broadcom, Mindspeed, Vitesse Semiconductors, AMCC, Exar Corporation, Conexant Systems, Marvell Technology Group, takođe i velike kompanije kao Agilent, Freescale, Intel IBM, Infineon, Motorola, Texas Instruments, Toshiba. • Vendori koji proizvode rutere i svičeve: Cisco, Juniper, Huawei, ZTE, Avici, Chiaro, Allied Telesyn i druge.

Skalabilnost • Skalabilni ruteri, odnosno ruteri velikog protoka, smanjuju broj tranzitnih portova, a samim tim: cenu mreže, kašnjenje i verovatnoću otkaza usled kompleksnosti mreže. • Dve funkcije su usko grlo u ruterima velikog kapaciteta: • IP lukap • Komutiranje paketa, odnosno ćelija

IP lukap • Najjednostavniji algoritam je trie algoritam koji se zasniva na stablu sa prefiksima IP adresa koji su mrežne adrese. • Najduži prefiks odgovara listu stabla, koji sadrži i ID izlaznog porta. • Stablo i portovi se čuvaju u brzoj memoriji, SRAM-u. • U najgorem slučaju broj pristupa memoriji je jednak dužini adrese, 32 kod IPv4 i 128 kod 128 IPv6. • Na 10Gb/s, najkraći paket je 50ns, a pristup memoriji traje 5-10ns.

Arhitektura komutatora (svičeva) • Paketski svičevi sa baferima na izlazu • Paketski svičevi sa zajedničkim baferom • Paketski svičevi sa baferima na ulazu • Birkoff-von-Neumannsvičevi • Torusni svičevi • Clos svičevi

Svičevi sa izlaznim baferima • Ako više paketa dolaze istovremeno za isti izlazni port, oni se memorišu u baferu tog izlaza. • U najgorem slučaju paketi sa svih ulaza dolaze na isti izlaz, te protok bafera mora biti jednak protoku sviča. • Protok sviča je ograničen protokom bafera. • Opsluživanje paketa u svakom baferu kontroliše poseban kontroler, ili skedžuler. Ovo omogućava visok kvalitet servisa: rezervacije kapaciteta, garancije kašnjenja i fer servis za saobraćaj najboljeg pokušaja.

Svičevi sa zajedničkim baferom • Svi paketi se upisuju u isti bafer i ispisuju iz istog bafera. • Protok bafera je dva puta veći od protoka sviča, ili protok sviča je duplo manji od maksimalnog protoka bafera. • Broj bafera visokog protoka je N puta manji, gde je N broj portova. • Opsluživanje paketa je takođe nezavisno pa se postiže isti kvalitet servisa, s tim što je memorija za čuvanje paketa po izlazu manja.

Svičevi sa ulaznim baferima • Kapacitet sviča se povećava kada su baferi na ulazu. Baferi više ne limitiraju protok sviča. • Paketi se iz ulaznih bafera šalju na izlaze kroz kros-bar. • Kros-bar je takav da u nekom trenutku ulaz šalje najviše jedan paket i izlaz prima najviše jedan paket. • Uzimajući u obzir funkcionisanje kros-bara, i informaciju o paketima u baferima, kontroler prosleđuje pakete kroz kros-bar. • Opsluživanje paketa postaje kompleksno, pa je teško ostvariti kvalitet servisa.

Birkoff-von-Neumannsvičevi • Paketi se segmentiraju na ćelije i te se ćelije prosleđuju kroz TDM svič na ulazu, u memorije. • Iz memorija se ćelije čitaju kada dođu na red za opsluživanje, opet kroz TDM svič, sada na izlazu. • Na svakom izlazu se odlučuje o redosledu opsluživanja ćelija, a prema TDM rasporedu. • Prednost je to što nije potreban centralni kontroler. • Mana je što može doći do katastrofalnog blokiranja. • O tome koliko je fer servis nema podataka.

Torusnisvičevi • Torusni svič je multistepeni. • Svaki ulazno-izlazni modul ima svoj svič preko koga je povezan sa 6 susednih ulazno-izlaznih modula. • Prednost ove arhitekture je da se lako proširuje. • Mana ovakvog sviča je da je blokirajući, i unosi dugo kašnjenje paketa. • Ne zna se ništa o tome koliko fer servis pruža ova arhitektura.

Clossvičevi • Clos svič je višestepeni svič, konkretno trostepeni. • Svičevi u ulaznom stepeni su povezani sa svičevima u srednjem stepenu koji su povezani sa svičevima u izlaznom stepenu. • Paketi su podeljeni na ćelije koje se balansiraju kroz svičeve u srednjem stepenu tako da su svi linkovi u sviču jednako opterećeni. • Ne postoji potreba za centralnim kontrolerom. • Može biti neblokirajući. • Ne zna se puno o tome koliko je opsluživanje paketa fer.

Transportni svičevi • Transportni svičevi komutiraju kola, što znači da alociraju fiksni kapacitet između portova. Ovaj fiksni kapacitet se zapravo sporo menja. • Transportni svičevi komutiraju SDH signale, koji u sebi nose ili TDM signale ili pakete. • Kompanije koje proizvode transportne svičeve su tradicionalni telekomunikacioni vendori i druge novije kompanije: Lucent, Siemens, Ericsson, Huawei, ZTE, NEC, Ciena, ali i domaća firma Iritel.

Paketsko procesiranje • Podrazumeva obradu paketa sve dok nije sačuvan u memoriju komutatora (sviča). • Najbolje razumevanje o pojedinim funkcijama se dobija kroz zaglavlja protokola koji se implementiraju.

LUKAP MEMORIJA PROCESOR FIZIČKOG SLOJA PROCESOR SLOJA LINKA MREŽNI PROCESOR BAFER BAFER MREŽNI PROCESOR PROCESOR SLOJA LINKA PROCESOR FIZIČKOG SLOJA Procesor fizičkog sloja POS-PHY-4, SPI-4 SFI-4 SFI-4 SerDes Framer Interface SPI-4 System Packet Interface je osnova za POS-PHY-4 (ili PL-4)

SDH (SONET) funkcije • TDM hijerarhija služi da se između rutera mogu obezbediti fleksibilni protoci. PDH (Plesio-chronous Digital Hierarchy) pruža kapacitete do 565Mb/s, a SDH do 40Gb/s. • Osnovno multipleksiranje je grubo, u PDH svaki sledeći nosioc ima 4 puta veći protok od prethodnog počev od E1 od 2Mb/s, kao i u SDH nosioci sadrže 1-1024 nosioca STM-1 sa protokom 155Mb/s. SONET ima nosioce sa 3,6,12,18,24,36,48,192, 468 i 3072 nosioca OC-1 sa protokom od 52Mb/s. • Kod SONET-a DS3=OC1, kod SDH E4=STM-1 • VCAT (Virtual Concetanation) i LCAS (Link Capacity Adjustment Scheme) se koriste da bi između rutera mogle da se dinamički obezbede flexibilni kapaciteti linkova. • SDH takođe omogućava da se otkriju problemi transmisije na linku, sekciji ili putanji.

VCAT i LCAS • VCAT omogućava fleksibilniju podelu kapaciteta nego SDH i to na različite načine. • Prvo, uzastopno sporiji nosioci mogu da se spoje i da im se dodeli kraće zajedničko zaglavlje, pri čemu se povećava efikasnost kanala. • Moguće je takođe da se spajaju nosioci koji nisu uzastopni, a koji su na raspolaganju, da bi se preneo kanal veće bitske brzine. Ovakva grupa nosioca se zove VCG (Virtual Concatenation Group). • LCAS je signalizacioni protokol sa kraja na kraj, sa dvostrukim rukovanjem, kojim se usklađuju kapaciteti predajnika i prijemnika.

Procesor fizičkog sloja • Prima signal, izdvaja takt iz njega, uobličava signal, uklanja smetnje, usaglašava fazu signala i vrši detekciju bita. • Vrši dekodovanje bita. • Ukoliko se paketi prenose preko TDM signala (PDH, SDH): procesor izdvaja zaglavlja, i vrši demultipleksiranje odnosno multipleksiranje. • Vrši konverziju signala u format potreban sledećem bloku.

LUKAP MEMORIJA PROCESOR FIZIČKOG SLOJA PROCESOR SLOJA LINKA MREŽNI PROCESOR BAFER BAFER MREŽNI PROCESOR PROCESOR SLOJA LINKA PROCESOR FIZIČKOG SLOJA Procesor sloja linka POS-PHY-4, SPI-4 SFI-4 SFI-4 SerDes Framer Interface SPI-4 System Packet Interface je osnova za POS-PHY-4 (ili PL-4)

Popularna zaglavlja sloja linka HDLC PPP Eternet

Popularna zaglavlja sloja linka • Popularni protokoli sloja linka su HDLC, PPP, i Eternet • Zajedničke polja su: flegovi, adresa destinacije, kontrolna suma za proveru ispravnosti okvira, i mrežni protokol. • HDLC ima i kontrolno polje kojom se određuje vrsta okvira (informacioni, nadzorni ili nenumerisani) koji obezbeđuje pouzdanost pomoću protokola sa klizećim prozorom. • PPP obično nema adresu destinacije. LCP (Link Control Protocol) okviri uspostavljaju i konfigurišu vezu. NCP (Network CP) okviri konfigurišu mrežni sloj. • Eternet ima i polje za dužinu paketa. PAUSE komande regulišu gustinu saobraćaja i šalju se na multikast adresu.

Procesiranje na sloju linka • Zajedničke funkcije za popularne slojeve linka su: • Razgraničavanje okvira pomoću flegova (kod Eterneta i dužine okvira) • Izdvajanje adrese destinacije i prijem okvira ako se adresa destinacije poklapa sa lokalnom adresom, • Provera ispravnosti okvira, • Određivanje mrežnog protokola. • Implementacija protokola klizećeg prozora kod HDLC protokola. • Obrada LCP i NCP okvira kod PPP protokola. • Obrada PAUSE okvira kod Eterneta. Popunjavanje okvira kod Gigabitnog Eterneta.

LUKAP MEMORIJA SDH FREJMER PROCESOR SLOJA LINKA MREŽNI PROCESOR BAFER BAFER MREŽNI PROCESOR PROCESOR SLOJA LINKA SDH FREJMER Mrežni procesor POS-PHY-4, SPI-4 SFI-4 SFI-4 SerDes Framer Interface SPI-4 System Packet Interface je osnova za POS-PHY-4 (ili PL-4)

Version (4 b) hdr lnth (4 b) TOS 1 2 total length pkt id 2 df mf (3 b) offset offset (cont’d) 1 1 TTL (time to live) Don’t Fragment More Fragments protocol hdr checksum 2 source 4 TCP, UDP destination 4 Variable (<40B) options padding variable IPv4 zaglavlje

vers TOS flow label (20 bits) (4 bits) (8 bits) payload length (2 B) Next (1 B) Hops (1 B) Source (128 bits) Destination (128 bits) hop by hop hdr, or dest info, or authentication hdr, or fragmentation hdr ... IPv6 zaglavlje

Procesiranje na mrežnom sloju • Zajedničke funkcije IPv4 i IPv6 su sledeće: određivanje prioriteta (polje ToS), razgraničavanje pakete preko njegove dužine, ažuriranje broja hopova, i izdvajanje IP adresa. • IPv4 obavlja dodatne funkcije provere ispravnosti zaglavlja, i segmentacije te rekonstrukcije paketa. • IPv6 ima u sebi adresu toka da bi pružio mogućnost uspostavljanja veze na ovom nivou. • Obe verzije pružaju razne opcije među kojima su najvažnije: eksplicitno zadavanje putanje i autentifikacija.

Procesiranje na mrežnom sloju • Mrežni procesor obavlja sledeće funkcije: • Određuje prioritet paketa i smešta ga u odgovarajući red za čekanje • Odbacuje paket ako je broj hopova veliki, u suprotnom inkrementira broj hopova • Izdvaja IP adresu destinacije, i vrši lukap • Proverava ispravnost zaglavlja (IPv4) • Vrši segmentaciju odnosno rekonstrukciju paketa (IPv4 ili IPv6 opcije) • Vrši autentifikaciju paketa, proveru integriteta paketa, dešifrovanje odnosno šifrovanje paketa (IPSec)

DRAM CPU CPU INTERFACE IP GMII Rx MAC SEGMENT. CHECK LOOKUP+ SRAM SGS CONT DRAM CONT. PHY SERDES SRAM CROSSBAR MAC GMII Tx REASSEM. Paketsko procesiranje: Primer implementacije

Paketsko procesiranje • Paket prima modul PHY, a zatim ga proverava modul MAC i predaje mrežnom modulu. • Mrežni procesor izdvaja iz IP zaglavlja važna polja, pre svega prioritet i IP adresu destinacije. • Mrežni modul na osnovu IP adrese određuje izlazni port konsultujući SRAM sa lukap tabelom. • Lukap tabelu se ažurira na osnovu informacije o topologiji mreže koju dobija iz centralnog procesora. CPU dobija OSPF pakete iz mrežnog procesora. • Paket se segmentira na ćelije jednake dužine, i na osnovu prioriteta i izlaznog porta paketa se smešta u SDRAM memoriju.