ALU

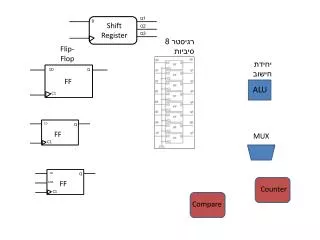

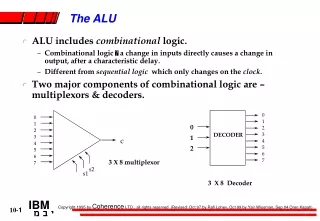

רגיסטר 8 סיביות. Flip-Flop. יחידת חישוב. 1D. 1D. 1D. Q. Q. Q. FF. FF. FF. ENA. Compare. Counter. C1. C1. C1. ALU. MUX. 1 Q. D. Shift Register. 2 Q. 3 Q. Decoder. sel. output. Decoder. Sel [0..0]. in. Out[1..0]. 0. input. Din valid. Output_0. Simple RAM.

ALU

E N D

Presentation Transcript

רגיסטר 8 סיביות Flip-Flop יחידת חישוב 1D 1D 1D Q Q Q FF FF FF ENA Compare Counter C1 C1 C1 ALU MUX 1Q D Shift Register 2Q 3Q

Decoder sel output Decoder Sel[0..0] in Out[1..0] 0 input Din valid Output_0 Simple RAM Data out clk 0 Data in Output[1..0] 1D 1D Q Q input Addr in FF FF Addr out Output_1 ENA ENA Dout valid Aout valid C1 C1 Simple RAM RAM data Din valid WE clk CLK Data in Data out DATA OUT DATA IN Addr in WADDR Addr out RADDR dout valid Aout valid

sel output Decoder input Addr out Data in RAM Addr in aout valid Generics Reset Clk Din valid Din valid Simple RAM Simple RAM Data out Data out clk clk Data in Data in Addr in Addr in Addr out Addr out Data in RC Dout valid Dout valid Aout valid Aout valid dout valid

REG_mux ‘0’ Trigger Type Reset Trigger Position Clk to start REG_input Enable Trigger Type Trigger Position Clk to start Enable Clk

Clk Reset RC finish Trigger found Dout valid 1D 1D 1D Q Q Q FF FF FF Addr to RAM Curraddr out Counter C1 C1 C1 Next addr out WC finish Start addr in ALU ALU Data from RAM Data to coordinate

‘0’ Data in Trigger Type Trigger Position ENABLE Reset Trigger Clk 1D 1D Q Q FF FF C1 C1 Trigger found Aout valid Data in RAM Addr in RAM ALU ALU Start Address next addr First addr Current addr

Data in valid Data in Reset Clk 1D Q FF C1 Data out valid Data out ALU