Understanding Delayed Branch in Computer Architecture: Challenges and Solutions

Delayed branching is a critical concept in computer architecture, affecting throughput and performance. This overview discusses the implications of delayed branches on assembly and compiler design, highlighting potential issues when incorporating loops and branch logic. We explore how delayed branches can lead to execution hazards, and the strategies to mitigate these problems. This resource aims to clarify the role of delayed branches within instruction sets and the coexistence of traditional and new branch types, ensuring a better understanding of optimizing critical paths in processing.

Understanding Delayed Branch in Computer Architecture: Challenges and Solutions

E N D

Presentation Transcript

Delayed Branch • All problems solved? NO, what will happen if...... b loop add $4 $6 $1 .. . loop sub

Add B loop Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend

sub Add B loop Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend

Delayed Branch - Throughput might decrease, (nop). - Assembler/Compiler dependent. + Keep critical path short

All problems solved now? NO, what will happen if...... .. bal loop add $4 $6 $1 xor .... loop: sub ... .. j $ra

bal loop Zeroext. = = Branch logic ADDR 0x00400004 0 A ALU 4 B + = = 31 + Sgn/Ze extend > ADDR 0x00400000 bal loop

bal loop add Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend ADDR 0x00400004 ADDR 0x00400000 bal loop > ADDR 0x00400004 add

bal loop sub add Zeroext. = = Branch logic ADDR 0x00400004 0 A ADDR 0x00400004 ALU 4 B + = = 31 + Sgn/Ze extend • ADDR 0x00400000 bal loop ADDR 0x00400004 add >loop: sub

jr $ra ADDR 0x00400004 Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend sub .. .. j $ra

Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend Oooh not again!!! 0x00400004 add

Continue at 0x00400008 bal loop sub add Zeroext. = = Branch logic ADDR 0x00400004 4 A ADDR 0x00400008 ALU 4 B + = = 31 + Sgn/Ze extend

jr $ra ADDR 0x00400008 Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend sub .. .. j $ra

All Hazards Fixed but: • One “delayed branch” slot

What about “delayed Branch” • Can we avoid it? • How?

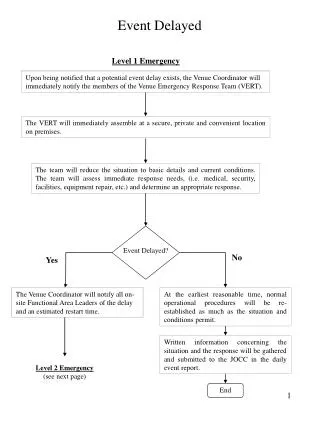

Delayed Branch Reg IM DM Reg Branch Logic Direct Branch Branch Logic Reg IM DM Reg

Delayed Branch Zeroext. = = Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend

Direct Branch Zeroext. = = Branch logic Branch logic 0 A ALU 4 B + = = 31 + Sgn/Ze extend

What about the instruction set? • beq $t0 $t0 label? • jr $ra? • NO, DE is not in path! • b label? • OK, but the new branch logic needs an ALU to compute the address

Different branch logic? • Can both branch types coexist? • Yes, no problem, but: • Old type still uses “delay slot”