NAND and NOR Gates

270 likes | 1.19k Views

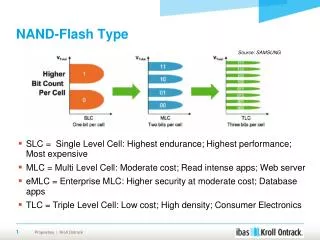

NAND and NOR Gates. ELEC 311 Digital Logic and Circuits Dr. Ron Hayne Images Courtesy of Cengage Learning. NAND and NOR Gates. DeMorgan's Laws. (X ∙ Y)' = X' + Y'. (X + Y)' = X' ∙ Y'. Functionally Complete Set. Any function can be realized using only NAND gates. SOP to NAND-NAND.

NAND and NOR Gates

E N D

Presentation Transcript

NAND and NOR Gates ELEC 311 Digital Logic and Circuits Dr. Ron Hayne Images Courtesy of Cengage Learning

NAND and NOR Gates 311_07

DeMorgan's Laws • (X ∙ Y)' = X' + Y' • (X + Y)' = X' ∙ Y' 311_07

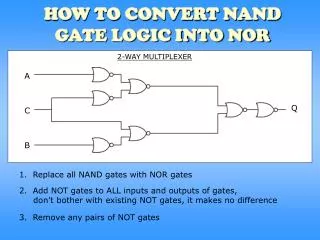

Functionally Complete Set • Any function can be realized using only NAND gates 311_07

SOP to NAND-NAND G = WXY + YZ 311_07

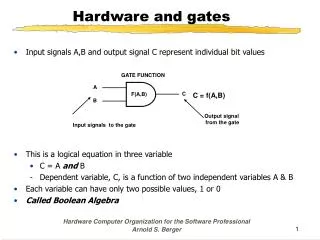

MOSFETs NMOS (n-channel) OFF ON PMOS (p-channel) ON OFF 311_07

CMOS Inverter 311_07

CMOS Inverter +V (H = 1) +V (H = 1) ON OFF OFF ON (L = 0) (L = 0) 311_07

CMOS NAND Gate (H = 1) (L = 0) 311_07

CMOS NAND Gate (H = 1) (L = 0) 311_07

CMOS NAND Gate (H = 1) (L = 0) 311_07

CMOS NAND Gate (H = 1) (L = 0) 311_07

CMOS NAND Gate (H = 1) (L = 0) 311_07

CMOS NOR Gate 311_07

VOHmin VIHmin VILmax VOLmax Noise Margin 311_07

Electrical Characteristics NMH = VOHmin - VIHmin = 4.4 V - 3.15 V = 1.25 V NML = VILmax - VOLmax = 1.35 V - 0.1 V = 1.25 V 311_07

Propagation Delay 311_07

Propagation Delay 311_07

Summary • NAND and NOR Gates • DeMorgan's Laws • SOP to NAND-NAND • MOSFETs • CMOS Logic Gates • Inverter, NAND, NOR • Electrical Characteristics • Noise Margin • Propagation Delay 311_07