The Processor: Datapath & Control

22343 - Computer Organization & Design. Chapter 5:. The Processor: Datapath & Control. Stored Program Architecture. Memory. Instructions (Program). Opcode Operands. Operands (Data). Binary Operand. PC. Instruction Cycle Fetch an instruction from memory Decode the instruction

The Processor: Datapath & Control

E N D

Presentation Transcript

22343 - Computer Organization & Design Chapter 5: The Processor:Datapath & Control

Stored Program Architecture Memory Instructions (Program) Opcode Operands Operands (Data) Binary Operand PC • Instruction Cycle • Fetch an instruction from memory • Decode the instruction • Get the operands • Execute the instruction • Where is the next instruction? Program Counter (PC) Instruction Pointer (IP) • Where is the operand?

ALU CPU CU Register File Datapath Control Unit

General-Purpose Register Organization Memory & I/O R1 R2 R3 R4 R5 R6 R7 MUX MUX ASEL BSEL 3 x 8Decoder A B OPR ALU DSEL

Memory & I/O R1 R2 R3 R4 R5 R6 R7 MUX MUX ASEL BSEL 3 x 8Decoder A B OPR ALU DSEL General-Purpose Register Organization Examples:

General-Purpose Register Organization Memory Instructions (Program) Trivial view of Opcode & Operands 00101 010 011 001 00 Operands (Data) 0000 0000 0000 0000 Examples:

Memory Interface Memory Memory 22 Byte│Byte│Byte│Byte 26 Byte│Byte│Byte│Byte Addr Read Data Write Data Data Address / Data Buses Read / Write Control Bidirectional /UnidirectionalData Bus

Building a Datapath Write a program & compile it. Where do you want to put it? Where is the first instruction? What comes out of memory? Where to perform operation? Where are the operands? Who well tell us which reg? Where to store result? Can we save this reg to mem? Opcode │ Operands Register File 32 32 32 PC Reg A (Read) Data A Addr Data B Reg B (Read) Data Reg C (Write) Instruction Memory Data C ALU Datapath Elements

Building a Datapath At what address? Register File PC Reg A (Read) Data A Addr Data Memory Data B Reg B (Read) Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Datapath Elements

Building a Datapath How can we read it back? Register File PC Reg A (Read) Data A Addr Data Memory Data B Reg B (Read) Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU

Building a Datapath Finished executing instruction. Where is the next instruction? Why +4? 4 Register File PC Reg A (Read) Data A Addr Data Memory MUX Data B Reg B (Read) Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder

Building a Datapath How can we add “immediate”? What if it is 8-bit negative? 4 Opcode │ Operand │ immediate Register File PC Reg A (Read) Data A Addr Data Memory MUX Data B Reg B (Read) Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder Sign Extend

Building a Datapath What about “JMP RelDisp”? It can be positive or negative! 4 Opcode │ Relative Displacement Register File PC Reg A (Read) Data A Addr Data Memory MUX Data B MUX Reg B (Read) Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder Sign Extend

Building a Datapath 4 Shift Left 2 Register File PC Reg A (Read) Data A Addr Data Memory MUX Data B Reg B (Read) MUX Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder Adder Sign Extend

Building a Datapath MUX Why the shift? 4 Shift Left 2 Register File PC Reg A (Read) Data A Addr Data Memory MUX Data B Reg B (Read) MUX Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder Adder Sign Extend Answer:

Building a Datapath MUX 4 Shift Left 2 Why not use ALU instead of another adder? Register File PC Reg A (Read) Data A Addr Data Memory MUX Data B Reg B (Read) MUX Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder Adder Sign Extend Answer:

Adding Control Signals to the Datapath 0 MUX 1 4 Shift Left 2 Register File PC Reg A (Read) Data A Addr Data Memory 1 MUX 0 Data B Reg B (Read) 0 MUX 1 Addr Data Data Reg C (Write) Instruction Memory Opcodeetc Data C Data ALU Adder Adder Control Unit Sign Extend Cy, Z, etc

Adding Control Signals to the Datapath 0 MUX 1 4 Shift Left 2 Register File PC Reg A (Read) Data A Addr Data Memory 1 MUX 0 Data B Reg B (Read) 0 MUX 1 Addr Data Data Reg C (Write) Instruction Memory Data C Data ALU Adder Adder Control Unit Sign Extend

A Simple Implementation Scheme 32 32 4 ALU Cntrl Cy Z 32 Cy = 1 Carry from last adder Z = 1 The result = 0 slt R1, R2, R3 ALU ALU Control

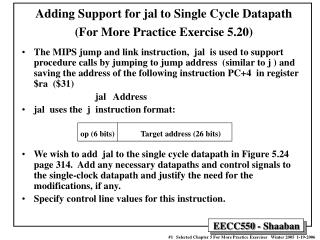

A Simple Implementation Scheme Instruction Opcode Operand(s), Address, Code 6 5 5 5 5 6 Rd = RsFunctRt 0 000000 Rs 00011 00111 Rt Rd 00101 00000 Shift Funct 100000 Register File Reg A (Read) Data A Data B Reg B (Read) Reg C (Write) Data C Example: • Instruction Format • Arithmetic/Logic

A Simple Implementation Scheme Instruction Opcode Operand(s), Address, Code 6 5 5 16 010000 001101 13 0 00000 00000 00001 00001 Rt 0000 0000 0000 1100 0000 0000 0000 0000 Immediate (Lower) Lower Rt = Value Upper Rt = Value 16 0 Rt Immediate (Upper) Example: R1 = 12 • Instruction Format • Load Immediate

A Simple Implementation Scheme Instruction Opcode Operand(s), Address, Code 6 5 5 16 35 100011 Rs 00100 00110 Rt 1111 1111 1111 1111 Address Rt = M [Rs + Addr] 32 bits 16 bits (can be positive or negative) Example: R6 = M [R4– 1 ] • Instruction Format • Load Memory

A Simple Implementation Scheme Instruction Opcode Operand(s), Address, Code 6 5 5 16 43 101011 Rs 00111 01001 Rt 1111 1111 1111 1110 Address M [Rs + Addr] = Rt Example: M [R7– 2 ] = R9 • Instruction Format • Store Memory

A Simple Implementation Scheme Instruction Opcode Operand(s), Address, Code 6 5 5 16 4 000100 Rs 00001 Rt 00100 1111 1111 1111 1111 Offset If Rs = Rt then PC = PC + 4*Addr PC is already incremented Example: • Instruction Format • JE Operation

Final Datapath Design 0 MUX 1 4 Shift Left 2 Register File Rs PC Reg A (Read) Data A Rt Addr Data Memory 1 MUX 0 Data B Reg B (Read) 0 MUX 1 Addr Data Data Rt MUX Reg C (Write) Rd Instruction Memory Data C Data ALU Adder Adder Offset, Addr, Immediate Sign Extend

Program Setup Example: Memory 001101 000000 000100 00000 00001 00001 00001 00001 00001 0000 0000 0000 1010 1111 1111 1111 1111 00001 00000 100000 0 4 8 3 4 0 1 0 0 0 A 0 0 2 1 0 8 2 0 1 0 2 1 F F F F Write a Program Assemble it Store it in Memory

Datapath Operation CLK PC I-Mem 0 ƮM Adder MUX PC Adder 0 1 ƮAdder RegASel 2 (Add) 10 0 10 10 4 RegCSel Reg CWrite ALU MUX ALU Ctrl Mem MUX Data A ƮReg Sign Ext 3401000A (LLI R1, 10) ALU ƮALU Data C Rs Rt Immediate ƮReg 13 0 1 10 Fetch Instruction Decode Instruction Get Operands Execute it

Datapath Operation CLK PC I-Mem 0 ƮM Adder MUX Ʈclk PC Adder 0 1 RegASel 4 2 (Add) 10 0 10 10 RegCSel Reg CWrite ALU MUX ALU Ctrl Mem MUX Data A ƮReg Sign Ext 3401000A (LLI R1, 10) ALU ƮALU Data C ƮReg How Fast Can the Clock Be?

Datapath Operation CLK PC I-Mem 0 4 Adder MUX PC Adder 4 1 1 RegASel 0 8 2 (Add) 10 10 20 20 RegCSel 1 Reg CWrite ALU MUX ALU Ctrl 2 Mem MUX Data A 0 Data B 00210820(Add R1,R1,R1) ALU 10 Data C 10 Rs Rt Rd Shift Funct 0 1 1 1 0 32 Fetch Instruction Decode Instruction Get Operands Execute it

Datapath Operation CLK PC I-Mem 4 8 PC Adder 8 1 1 PC Adder 2 Adder MUX 12 8 6 (Sub) 20 20 0 RegASel 1 RegCSel 1 Reg CWrite ALU MUX ALU Ctrl 2 Data A 10 Data B 10 1021FFFF (JE R1,R1,-1) ALU 20 Rs Rt Offset 4 1 1 – 1 Fetch Instruction Decode Instruction Get Operands Execute it

Datapath Operation CLK PC I-Mem 4 8 ƮM PC Adder 8 1 1 PC Adder 2 Adder MUX 12 8 6 (Sub) 20 20 0 RegASel 1 RegCSel 1 Reg CWrite ALU MUX ALU Ctrl 2 Data A 10 ƮReg Data B 10 1021FFFF (JE R1,R1,-1) ALU 20 ƮALU How Fast Can the Clock Be?

Datapath Operation CLK PC I-Mem 4 8 ƮM PC Adder 8 Ʈclk ƮAdder 1 1 PC Adder 2 ƮAdder Adder MUX 12 8 6 (Sub) 20 20 0 RegASel 1 RegCSel 1 Reg CWrite ALU MUX ALU Ctrl 2 Data A 10 ƮReg Data B 10 1021FFFF (JE R1,R1,-1) ALU 20 ƮALU How Fast Can the Clock Be?

Single-Cycle Implementation CLK PC I-Mem i RegASel 3 RegCSel 4 Reg CWrite 2 (Add) 7 d d+7 v v ALU MUX ALU Ctrl Mem MUX Data A Sign Ext ALU D-Mem 8C640007(LD R4,[R3+7]) Data C Rs Rt Address 35 3 4 7 Fetch Instruction Decode Instruction Get Operands Execute it

Single-Cycle Implementation CLK PC I-Mem i ƮM RegASel Ʈclk 3 RegCSel 4 Reg CWrite 2 (Add) 7 d d+7 v v ALU MUX ALU Ctrl Mem MUX Data A ƮReg Sign Ext ALU ƮALU D-Mem ƮM 8C640007(LD R4,[R3+7]) Data C ƮReg Clock Speed?

Single-Cycle Implementation Load Immediate/ALU: Ʈclk>ƮM+2ƮReg+ ƮALU Load Memory: Ʈclk>2ƮM+2ƮReg+ ƮALU Store Memory: Ʈclk>2ƮM+ƮReg+ ƮALU Conditional Jump: Ʈclk>Max ƮM+ƮReg+ƮALU 2ƮAdder Ʈclk=ps GHz Example: ƮM= 200 picoseconds ƮALU = 100 picoseconds ƮAdder = 100 picoseconds ƮReg= 50 picoseconds Fastest Clock?

Multicycle Implementation Register File X IR Reg A (Read) Data A PC Memory Reg B (Read) Result Addr Reg C (Write) Y Data B MDR Data C ALU Data Data Instructions take different number of clock cycles Functional units can be shared within the execution of a single instruction

Multicycle Implementation IR X PC Register File Result Reg A (Read) Data A Y 4 Memory Reg B (Read) MDR Addr Reg C (Write) Data B Sign Extend Data C ALU Shift Left 2 Data Data Exercise: Can you do all the previous instruction here? Some registers are not visible to the programmer

Multicycle Implementation 0 1 2 3 0 1 IR X 0 1 0 1 0 1 0 1 Memory Register File Result PC Reg A (Read) Data A Y 4 Reg B (Read) MDR Addr Reg C (Write) Data B Data Sign Extend Data C ALU Shift Left 2 Data Some registers are not visible to the programmer

Multicycle Datapath Operation 1 CLK PC 0 MemRd Ʈclk IRLD IR Mem Out 4 ƮM X MUX Y MUX 0 ALU Ctrl 2 (Add) ALU ƮALU PCMUX PCLD 3401000A Fetch Instruction

Multicycle Datapath Operation 2 CLK PC 0 4 MemRd IRLD 0 IR 3401000A (LLI R1, 10) Mem Out 10 0 Ʈclk RegASel XLD X Data A ƮReg Sign Ext Rs Rt Immediate 13 0 1 10 Fetch Instruction Decode Instruction Get Operands

Multicycle Datapath Operation 3 CLK PC 4 IR 3401000A (LLI R1, 10) XLD X 0 X MUX 10 Y MUX 2 ALU Ctrl 2 (Add) Ʈclk ResultLD Result ALU ƮALU Rs Rt Immediate 13 0 1 10 Fetch Instruction Decode Instruction Get Operands Execute it

Multicycle Datapath Operation 4 CLK PC 4 IR 3401000A (LLI R1, 10) ResultLD Result 10 RegCSel 1 C MUX Reg CWrite Ʈclk ƮReg Ʈclk Rs Rt Immediate 13 0 1 10 Fetch Instruction Decode Instruction Get Operands Execute it

Multicycle Datapath Operation CLK PCLD PC 0 4 MemRd Mem Out IRLD 3401000A IR 3401000A (LLI R1, 10) RegASel 0 Data A 0 XLD X 0 Sign Ext 10 ALU Ctrl 2 (Add) 2 (Add) ALU 4 10 ResultLD Result 10 RegCSel 1 RegCWrite Rs Rt Immediate IR M[PC] PC PC + 4 X Reg[IR[25:21]] Rs R X+IR[15:0] Immediate Reg[IR[20:16]] R Rt . 13 0 1 10

Multicycle Datapath Operation CLK PCLD PC i i+4 MemRd Mem Out IRLD instruction IR instruction RegASel Rs Selection Data A Rs XLD X Rs Sign Ext value ALU Ctrl Add Add Opcode ALU i+4 i+4+disp result ResultLD Result i+4+disp result RegCSel Rd Rt RegCWrite ALU Operation: R X op Y R X op IR[16:0] LD Operation: Reg[IR[20:16]] MDR. X Reg[IR[25:21]] Y Reg[IR[20:16]] R PC+IR[16:0]] IR M[PC] PC PC + 4 Reg[IR[15,11]] R MDR Mem[R] Mem[R] Y

Multicycle Implementation Load Immediate/ALU: 4 Clocks Load Memory: 5 Clocks Store Memory: 4 Clocks Conditional Jump: 3 Clocks On Average: CPI = Instr. Exec. Time = ps Ʈclk= GHz Example: ƮM= 200 picoseconds ƮALU = 100 picoseconds ƮAdder = 100 picoseconds ƮReg= 50 picoseconds Fastest Clock?

Control Implementation Datapath Control Signals: ALU Operation, MUX Selection,Memory Rd/Wr, etc Control Unit CU Data Processing Unit DPU or Datapath • • • • • • Datapath Status Signals: IR Fields, ALU Flags

Control Implementation • Hardwired • Standard Logic Components • Fast • Not Flexible, i.e. Difficult to Change Control Operation • Microprogrammed • Memory-Based • Speed Function of Memory (slower than hardwired) • Flexible Design

Control Implementation Control Unit CombinationalControlLogic Datapath Control Outputs • • • • • • • • • State Register Datapath Control inputs • • • • Hardwired • FiniteStateMachine

Microprogrammed Control Implementation Control Unit Microprogram Counter Microprogram Memory (Microstore) ALU Operation, MUX Selection,Memory Rd/Wr, etc Each Linein the Micro-ProgramExecutesMicro-Operations(in 1 Clock) Fetch,Decode,ExecuteCycle

Microprogram Control Unit Datapath Control Signals: