Appearance-based Equivalence Checking

Appearance-based Equivalence Checking. Speaker: Ching -Yi Huang Advisor: Chun-Yao Wang Date: 2011/07/20. Outline. Introduction Approach Methodology Overview Observation and Transformation Rules Error Injection-based Rewiring (EIR) Circuit Optimization Equivalence Checking Flow Chart

Appearance-based Equivalence Checking

E N D

Presentation Transcript

Appearance-based Equivalence Checking Speaker: Ching-Yi Huang Advisor: Chun-Yao Wang Date: 2011/07/20

Outline • Introduction • Approach • Methodology • Overview • Observation and Transformation Rules • Error Injection-based Rewiring (EIR) • Circuit Optimization • Equivalence Checking • Flow Chart • Future work

Introduction • What is equivalence checking? • Given: • Two combinational circuits. Golden circuit and revised circuit. • Objective • Check whether the functionality of two given combinational circuits are equivalent.

Introduction • Functionality equivalence I1 O1 C1 Im On o1 C2 on

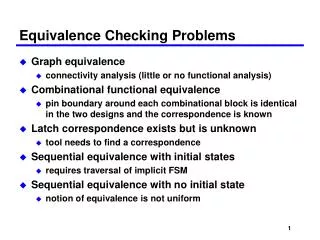

Introduction • Traditional methods • Truth table • BDD-based • ATPG-based • SAT-based

Motivation • Appearance-based approach • Don’t build BDDs • If two circuits are equivalent, there should be a rule to transform their appearances into the same one.

Problem Formulation Appearance-based approach equivalence checking • Given: • Two combinational circuits. Golden circuit and revised circuit. • Objective • Observe their appearances • According to the rules, transform the appearance (by rewiring techniques) of one circuit into a new circuit which is the same as the other.

Problem Formulation • If their appearances are the same, they are functionally equivalent. • If their appearances are not the same: • we can reduce the number of PIs • we can reduce the size of the circuit that requires doing traditional equivalence checking.

Outline • Introduction • Approach • Methodology • Overview • Observation and Transformation Rules • Error Injection-based Rewiring (EIR) • Circuit Optimization • Equivalence Checking • Flow Chart • Future work

Overview An action per round For eliminating the rectification networks

Structure • AIG = AND-Inverter Graph • DAG = Direct Acyclic Graph • Two Inputs AND gate node • Inverter on the edge B C F A

Outline • Introduction • Approach • Methodology • Overview • Observation and Transformation Rules • Error Injection-based Rewiring (EIR) • Circuit Optimization • Flow Chart • Implementation • Correctness Verification • Circuit Simplification • Experiment Results • Future work

Concept • Examples of our concept Revised Golden B B C A F F A C

Concept • Goal: Make sure that two circuits have the same nodes in the same level . • Look at the nodes of the same level. • Try to preserve the positions of original nodes • If we can just change the input phases or input wires to achieve that goad, then do it. B B C A F F A C

How to make the IDs consistent • After transforming, give the nodes new TIDs.

Observation & Rules • Observation: • Observe the revised circuit and golden circuit by an sequence that can include all conditions. • Rules: • After observing one condition, we do some actions.

Observation M K I G D F B B M D C C E L E H A J L A

Observation & Rules • 1. Same node (has same fanins and same fanin phases) • Never change B B Revised Golden A A

Observation & Rules • 2. Different phase • Action: Gate replacement D D Revised Golden C C

Observation & Rules • 3. Change one fanin Revised F G G Golden E E E E (1) removal (2) addition

Observation & Rules • After 1~3, if there are still some nodes which are not dealt with in both circuits… • First consider - 4. Change two fanins I K H J Revised Golden

Observation & Rules Revised Golden • 4. Change two fanins T2 T1 K K I K H J J J T2 T1 (1) Remove fanouts T2 T1 (2) Create the new node T2 or T1

Observation & Rules • After 1~4, there are two conditions • (1) There is no node which is not dealt with Done! • (2) There are some nodes in one of these circuits • Consider 5. Delete surplus node/ Create necessary node

Observation & Rules • 5-1 Delete surplus node Revised Golden T2 M T1 NULL L (1) Remove fanouts T2 T1

Observation & Rules • 5-2 Create necessary node M M Golden Revised L L NULL (1) Create the new node

Problems of Level Information change Revised F G G Golden E E E E (1) removal (2) addition

Problems of Level Information change • How about multiple fanouts Revised F G G Golden T1 E E E T2 E T3 T1 T1 ? (1) removal (2) addition ? T2 T2 T3 T3

Problems of Level Information change • What we want is just the specific node. • To save efforts, we won’t do addition on every fanout wires. • However, due to the removal action, the levels of some fanout nodes would be decreased. • New levels can’t be lower than or equal to the current level. F E T1 T1 E T2 T2 T3 T3

Problems of Level Information change • Statically analyze the level of the side input node of the fanout nodes and the level of fanout nodes. • (1) levelfanout == levelcurrent +1 • (2) levelfanout > levelcurrent +1 F E T1 T1 E T2 T2 T3 T3

Problems of Level Information change • (2) levelfanout > levelcurrent +1 • Need to consider if the side input node is in the TFOC of current node. F E T1 T1 E T2 T2

Problems of Level Information change • How about 4. change two fanins • Solution: Be modeled as “change one fanin” problem. I K Revised Golden T2 T1 H J T3 T4 T5 T6

Problems of Level Information change • How about 5-1. delete surplus node • Solution: Modeled as “change one fanin” problem and choose one node which has TID in current level to do addition. I Revised Golden T2 T1 H NULL T3 T4 T5 T6

Problems of Level Information change • If there is no fanout wire needs addition? • For 3.change one fanin – the new node must be created. • We must choose at least one fanout wire to do addition. F Revised E T1 E E T2 T1 T1 T3 (1) removal (2) addition T2 T2 33 T3 T3

Problems of Level Information change • If there is no fanout wire needs addition? • For 4.change two fanins – we have created the wanted node. • For 5. delete surplus node – YA!

Observation M K I G D F B B M D C C E L E H A J L A

Outline • Introduction • Approach • Methodology • Overview • Observation and Transformation Rules • Error Injection-based Rewiring (EIR) • Circuit Optimization • Equivalence Checking • Flow Chart • Future work

EIR • Error Modeling • Removal • Addition • Replacement • Propagate fault • Find TAs • Choose destination • Rectification

Model the errors (AIG format) • Remove wire

Model the errors (AIG format) • Add wire a a a a b b

Model the errors (AIG format) • Replacement

Model the errors (AIG format) • Replacement

EIR • Destination Ⅱ Ⅰ Ⅲ error effect . . . . . .

EIR Algorithm • Region I/II • DON/DOFF = AND(TA) • If the error effect propagated to gd is 1/0, the corrected function for the error effect is • If the error effect propagated to gd is 0/1, the corrected function for the error effect is • If both 1/0 and 0/1 error effects are propagated to gd, the corrected function is either or

EIR Algorithm • Region III gdg(TA)= the cofactor of gd with respect to TA in good circuit • DON: • DOFF: • Corrected function: or

Rectification Issue • Choose where?

Choose the PO as destination • Choose the PO as destination!? • PO is the common dominator! B C D A E F G

More destination Issues • More convenient => larger rectification networks • Destination: • Still choose dominators as destinations. • May not always choose POs as the destinations.

Outline • Introduction • Approach • Methodology • Overview • Observation and Transformation Rules • Error Injection-based Rewiring (EIR) • Circuit Optimization • Equivalence Checking • Flow Chart • Future work

Rectification networks Revised Golden B B(T1) T4 A F T5 C(T2) F A(T3) C T1 T4 T5 T2 F T3 Rectification networks

Optimization • Node-merging w1 w1 w2 w2 nt nt w3 w3 w4 ns ns w4