Xilinx Virtex-4

500 likes | 624 Views

Universidade Estadual de Campinas MO801 – Tópicos em Arquitetura e Hardware Professor Dr. Rodolfo Jardim de Azevedo. Xilinx Virtex-4. Vinícius José Latorre viniciusjl@gmail.com RA 781081 1S 2006. Índice. Visão Geral Funcionalidades Blocos de I/O (IOBs)

Xilinx Virtex-4

E N D

Presentation Transcript

Universidade Estadual de Campinas MO801 – Tópicos em Arquitetura e Hardware Professor Dr. Rodolfo Jardim de Azevedo Xilinx Virtex-4 Vinícius José Latorre viniciusjl@gmail.com RA 781081 1S 2006

Xilinx Virtex-4 Vinicius Índice • Visão Geral • Funcionalidades • Blocos de I/O (IOBs) • Blocos Lógicos Configuráveis (CLB) • Blocos de RAM • XtremeDSP • Clock • Clock global e regional • Blocos DCM (Digital Clock Manager) • Blocos PMCD (Phased Matched Clock Dividers) • RocketIO • PowerPC 405 • Core Ethernet MAC • Referências Bibliográficas

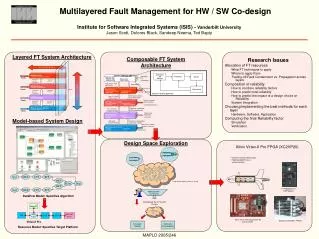

Xilinx Virtex-4 Vinicius Visão Geral • Virtex-4 compreende um conjunto de famílias de FPGAs • Virtex-4 LX: aplicações de alto desempenho • Virtex-4 SX: aplicações DSP (Digital Signal Processing) de alto desempenho • Virtex-4 FX: solução completa e de alto desempenho para aplicações de plataformas embutidas • Componentes do Virtex-4 são uma melhoria dos já existentes em outras famílias (Virtex, Virtex-E, Virtex-2, Virtex-2 Pro e Virtex-2 Pro X) • compatibilidade upward

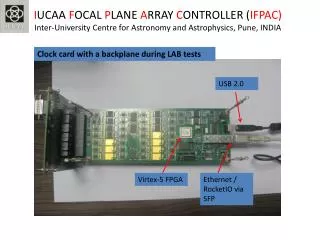

Xilinx Virtex-4 Vinicius Visão Geral (cont.) • Todos os dispositivos Virtex-4 implementam as funcionalidades: • Blocos de I/O (IOBs): interface entre os pinos e a lógica interna • Blocos lógicos configuráveis (CLBs): elementos lógicos básicos • Blocos de RAM: 18Kbit true dual-port RAM • XtremeDSP slices • Blocos DCM (Digital Clock Manager) • Somente os dispositivos Virtex-4 FX suportam: • RocketIO MGT (Multi-Gigabit Transceiver) • CPU RISC embutida IBM PowerPC 450 (450 MHz) • Cores EMAC (Ethernet Media Access Control) de 10/100/1000 Mb/s

Xilinx Virtex-4 Vinicius Visão Geral (cont.) • Matriz geral de rotas (GRM) fornece um vetor de chaves de roteamento entre os componentes. • Cada elemento programável é acoplado a uma matriz de chaves, que permite múltiplas conexões com a GRM. • O conjunto de interconexões programáveis é hierárquico. • Todos os elementos programáveis, incluindo os recursos de roteamento, são controlados por valores armazenados em células de memória estática. • Os valores são carregados nas células de memória durante a configuração.

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – IOB Básico (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – IOB Básico (cont.) • Suporta os padrões single-ended: LVTCL, LVCMOS, PCI, PCIX, GTL, GTLP, HSTL e SSTL • Suporta os padrões de I/O diferencial: LVDS, BLVDS, ULVDS, HyperTransport, HSTL diferencial e SSTL diferencial • DCI (Digitally Controled Impedance) I/O pode ser configurado para prover terminação on-chip para cada padrão single-ended e alguns diferenciais • 2 ou 4 blocos de I/O se conectam a uma matriz de chaves para acessar os recursos de roteamento • O circuito de per-bit deskew possibilita um atraso programável do sinal interno à FPGA. Útil para sincronização de sinais em interfaces sincronizadas pela fonte

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – IOB Básico (cont.) • As entradas dos clocks regionais são distribuídas dentro de uma região limitada para minimizar o atraso de clock entre IOBs • Clocks regionais de I/O suplementam os recursos de clock global • Serializadores/deserializadores de dados são adicionados a cada I/O para suportar interfaces sincronizadas pela fonte • Um conversor serial para paralelo (com o divisor de clock associado) é adicionado no caminho de entrada • Um conversor paralelo para serial é adicionado no caminho de saída

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – ILOGIC (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – ILOGIC (cont.) • ILOGIC contem: • 4 elementos de armazenamento (IFF1, IFF2, IFF3, IFF4) • 1 elemento programável de atraso (IDELAY) • IDELAY é um elemento de atraso (64-tap, wraparound) com uma resolução fixa e garantida de tap • O registrador IFF1 pode ser usado para construir um flip-flop D • O registrador IFF1 é o único que pode ser configurado como level-sensitive latch • Os registradores IFF2, IFF3 e IFF4 são usados para se constuir vários registradores DDR (Double Data Rate) de entrada • IDDR (Input DDR) tem os modos: OPPOSITE_EDGE, SAME_EDGE e SAME_EDGE_PIPELINED

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – OLOGIC (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – OLOGIC (cont.) • OLOGIC contem 6 elementos de armazenamento: • 3 registradores (TFF1, TFF2, TFF3) são usados para o controle 3-state • 3 registradores (OFF1, OFF2, OFF3) são usados para a saída de dados • Os registradores OFF1/TFF1 podem ser usados para se construir um flip-flop D • Os registradores OFF1/TFF1 são os únicos que podem ser configurados como level sensitive latch • Os registradores OFF2/TFF2 e OFF3/TFF3 são usados para se construir vários registradores DDR de saída

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – OLOGIC (cont.) • Os registradores OFF1, OFF2 e OFF3 compartilham um clock enable (OCE) comum • Os registradores TFF1, TFF2 e TFF3 compartilham um outro clockenable (TCE) • Todos os registradores OLOGIC têm um clock comum e, set e reset síncrono ou assíncrono • ODDR (Output DDR) tem os modos: OPPOSITE_EDGE e SAME_EDGE

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – ISERDES (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – ISERDES (cont.) ISERDES (Input serial-to-parallel) contem: • Conversor serial para paralelo dedicado • Permite transferência de dados a alta velocidade • Suporta SDR (Single Data Rate) • Cria palavras de 2, 3, 4, 5, 6, 7 ou 8 bits paralelos • Suporta DDR (Double Data Rate) • Cria palavras de 4, 6, 8 ou 10 bits paralelos • IDELAY é um elemento de atraso (64-tap, wraparound) com uma resolução fixa e garantida de tap • Modos de operação: DEFAULT (sem atraso), FIXED e VARIABLE

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – ISERDES (cont.) • O submódulo BITSLIP permite reordenar a seqüência do stream de dados paralelos; serve para treinar interfaces sincronizadas pela fonte que tenham padrão (pattern) de treinamento • Suporte dedicado para interfaces de memória strobe-based • Suporte dedicado para networking interfaces

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – OSERDES (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de I/O (IOB) – OSERDES (cont.) OSERDES contem: • Recurso de clock e lógica projetada para facilitar a implementação de interfaces sincronizadas pela fonte de alta velocidade • Serializador de dados dedicado de até 6:1 (SDR ou DDR) • 10:1 se usar OSERDES width expansion • Controlador de 3-state (SDR ou DDR) • Serialização de até 4:1

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco Lógico Configurável (CLB) • Recurso para implementar circuitos seqüênciais ou combinatoriais • Cada CLB é conectada a uma matriz de chaves para acessar a GRM • Cada CLB contem 4 slices interconectados, agrupados em pares; cada par é organizado em uma coluna: • SLICEM: par de slices da coluna à esquerda • SLICEL: par de slices da coluna à direita • Cada par em uma coluna tem um carry chain independente • Somente SLICEM tem um shift chain comum

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco Lógico Configurável (CLB) (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco Lógico Configurável (CLB) (cont.) • SLICEM & SLICEL • 2 LUTs de 4 entradas (geradores de função) • Cada gerador de função pode implementar uma ROM de 16, 32, 64, 128 e 256 bits • 2 elementos de armazenamento • Podem ser flip-flop D ou level sensitive latch • Sinais comuns de clock, clockenable e set/reset • Multiplexadores amplos (MUXF5, MUXF6, MUXF7, MUXF8) • Usados para combinar até 8 geradores de função para prover qualquer função de 5, 6, 7 ou 8 entradas • Podem combinar LUTs dentro da mesma CLB ou entre CLBs • Carry logic • Provê adição e subtração aritmética rápida • 2 bits por slice • Portas aritméticas • XOR permite adicionador de 2 bits • AND melhora a eficiência da implementação de multiplicadores

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco Lógico Configurável (CLB) (cont.) • SLICEM • Armazena dados usando RAM distribuída • LUTs combinadas para armazenar dados (memória) • Síncrono • Shift dos dados com registradores de 16 bits • Implementado pela configuração dos geradores de funções • Cada LUT pode atrasar o dado serial de 1 até 16 ciclos e 64 ciclos em uma CLB • Usado para balancear o timing dos pipelines de dadosAplicações que requerem compensação de atraso ou latênciaProjetos FIFO síncrono ou CAM (Content Addressable Memory) • Qualquer um dos 16 bits pode ser lido assincronamente pela variação do endereço da LUT • Conexão dedicada entre o último bit de um shift register e o primeiro bit do próximo

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de RAM • Similar ao bloco de RAM do Virtex-2 e Spartan-3 • Cada bloco armazena 18 Kbits de dados • Leitura e escrita síncronas • Portas simétricas e independentes • Compartilham somente o dado armazenado • Pode ser configurado para 16Kx1, 8Kx2, até 512x36 (portas independentes) • Conteúdo de memória pode ser definido/limpado pelo bitstream de configuração • Durante a escrita, a saída pode ser o dado sendo escrito, o dado anterior a escrita, ou permanece inalterado • True dual-port RAM

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de RAM (cont.) Melhoramentos do Virtex-4: • Registradores pipeline na saída de leitura dos dados (taxa de clock mais alta ao custo de 1 período de clock de latência) • 2 blocos de RAM adjacentes podem ser combinados (32Kx1) sem lógica adicional ou perda de velocidade • Portas de 18 ou 36 bits com write enable individual por byte (usado para interfacear com PPC450) • Cada bloco de RAM contem sequenciamento de endereço e circuito de controle com uma built-in multirate FIFO memory • FIFO pode ser 4Kx4, 2Kx9, 1Kx18 ou 512x36 • Portas de leitura e escrita têm a mesma largura • Os 2 clocks podem ter freqüências diferentes (assíncronos entre si) • Operação é controlada pelas entradas read e write enable • Não requer CLB adicional para o controle da FIFO

Xilinx Virtex-4 Vinicius Funcionalidade: Bloco de RAM (cont.) Adiconalmente • Porta de saída é latched • Toda entrada é registrada com a porta clock • Toda saída tem uma função read ou read-during-write • Operação de escrita requer um clockedge • Operação de leitura requer um clockedge

Xilinx Virtex-4 Vinicius Funcionalidade: XtremeDSP Slice

Xilinx Virtex-4 Vinicius Funcionalidade: XtremeDSP Slice (cont.) • Suporta conexão de múltiplos DSP48 slices para formar funções matemáticas, filtros DSP e aritmética complexa sem o uso de outros recursos da FPGA • Pipeline programável das entradas dos operandos, produtos intermediários e saídas do acumulador • Bus interno de 48 bits • Número de DSP48 slices por família • LX: 32, 48, 64, 80, 96 • SX: 128, 192, 512 • FX: 32, 48, 128, 160, 192

Xilinx Virtex-4 Vinicius Funcionalidade: XtremeDSP Slice (cont.) • Multiplicador de 18 bits x 18 bits seguido por multiplexadores e adder/subtracter de 3 entradas • Multiplicador aceita 2 operandos de 18 bits e complemento de 2 e produz um resultado de 36 bits e complemento de 2 • O resultado tem sinal extendido até 48 bits e pode ir para o adder/subtracter • O adder/subtracter aceita 3 operandos de 48 bits com complemento de 2 e produz um resultado de 48 bits • O resultado do adder/subtracter pode ser registrado num acumulador

Xilinx Virtex-4 Vinicius Funcionalidade: Clock – Global e Regional • 8 a 24 regiões de clock, dependendo do tamanho do dispositivo Clock global • 32 linhas matched-skew que servem todo dispositivo (CLB, bloco de RAM, DCM e I/O) e direcionam os sinais lógicos • Quaisquer 8 das 32 linhas globais podem ser usadas em qualquer região • As linhas globais de clock são dirigidas somente por um buffer de clock global • Pode selecionar entre 2 fontes de clock • Pode chavear de uma fonte falha de clock (Virtex-4) • Buffer de clock global é dirigido pelo DCM para eliminar o atraso na distribuição do clock ou para ajustar o atraso relativo a um outro clock • Há mais clocks globais do que DCMs, mas um DCM governa mais do que um clock global

Xilinx Virtex-4 Vinicius Funcionalidade: Clock – Global e Regional (cont.) Clock regional e clocks de I/O • Cada região tem 2 entradas “clock capable” • Cada entrada pode single-ended ou diferencialmente dirigir clocks regionais e clocks de I/O na mesma região, e na região abaixo ou acima (até 3 regiões adjacentes) • O buffer de clock regional pode ser programado para dividir a taxa de clock de entrada por 1 a 8 • Em conjunção com o serializador/deserializador programável no IOB, permite que sistemas sincronizados pela fonte cruzem os domínios de clock sem o uso de lógica adicional • Clocks de I/O são muito rápidos e servem circuitos locais de serialização/deserialização de I/O

Xilinx Virtex-4 Vinicius Funcionalidade: Clock - Bloco DCM (Digital Clock Manager) • Clock deskew • DCM contem um DLL (Delay-Locked Loop) para eliminar o atraso na distribuição do clock • DLL contem elementos de delay (pequenos buffers) e lógica de controle • O clock de entrada direciona uma cadeia de elementos de delay • A lógica de controle contem um detector de fase e um seletor delay-line • Síntese de freqüência • Saídas separadas fornecem uma freqüência dobrada (CLK2X e CLK2X180) • Outra saída (CLKDV) fornece uma freqüência que é uma fração da freqüência de entrada • 2 outras saídas (CLKFX e CLKFX180) fornecem uma freqüência de saída derivada do clock de entrada pela divisão e multiplicação simultânea de freqüência

Xilinx Virtex-4 Vinicius Funcionalidade: Clock - Bloco DCM (Digital Clock Manager) (cont.) • Phase shifting (2 tipos) • Baixa resolução • Usa as fases de 90º, 180º e 270º de CLK0 para fazer as saídas de clock CLK90, CLK180 e CLK270 • Alta resolução • Permite que toda saída de clock do DCM seja phase-shifted relativo a CLKIN enquanto mantem a relação entre as saídas de baixa resolução • Reconfiguração dinâmica • Há uma conexão do bus com o DCM para se mudar os atributos do DCM sem reconfigurar o resto do dispositivo • 4 modos: FIXED, VARIABLE_POSITIVE, VARIABLE_CENTER e DIRECT

Xilinx Virtex-4 Vinicius Funcionalidade: Clock - Bloco DCM (Digital Clock Manager) (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Clock – PMCD (Phase-Matched Clock Dividers) Tem os seguintes gerenciamentos de clock: • Phase-matched divided clocks • PMCDs criam até 4 versões frequency-divided e phase-matched de uma entrada de clock (CLKA) • Phase-matched delay clocks • PMCDs preservam os alinhamentos de borda, relações de fase ou atraso entre o clock de entrada CLKA e os outros clocks PMCD de entrada

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – RocketIO MGT • Taxa de dados de 622 Mb/s até 10.3125 Gb/s • 8 a 24 transceiver por FPGA • 3-tap transmitter pre-emphasis (pre-equalization) • Receiver continuous time equalization • Equalizador DFE (Decision Feedback Equalizer) para aplicações legado backplane • Optional on-chip AC coupled receiver • Digital oversampled receiver para taxa de dados de até 1.25 Gb/s • Receiver signal detect, loss of signal indicator, OOB (out-of-band) signal receiver • Codificação 8B/10B ou 64B/66B ou nenhuma codificação (pass-through mode) • Chanel bonding • Geração e verificação de CRC (Cyclic Redundancy Check) flexível • Reconfiguração pelo usuário através da porta de reconfiguração dinâmica (DRP)

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – IBM PowerPC 450 • PowerPC é uma arquitetura 64 bits com um subconjunto de 32 bits

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – IBM PowerPC 450 (cont.) • PowerPC 450 (PPC450) é um processador de 32 bits que é uma implementação do PowerPC embedded environment architecture que é derivada da arquitetura PowerPC • Aplicações embarcadas para o PPC450 são compatíveis com outras implementações de PowerPC • Bloco do processador é uma combinação: • Core PPC405D5 (Virtex-2 Pro) ou PPC405F6 (Virtex-4) • On-chip memory logic (OCM) • Controlador APU (Auxiliary Processor Unit) (Virtex-4) • Mais lógica e interface

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – IBM PowerPC 450 (cont.) • Unidade de ponto fixo com 32 registradores de propósito geral de 32 bits • Extensão à embedded environment architecture: • Operação true little-endian • Gerenciamento de memória flexível • Instruções multiply-accumulate • Capacidade de depuração • 64 bits time base • 3 timers (sincronizados com o time base): PIT, FIT, watchdog • Capacidade para melhoria de desempenho: • Static branch prediction • Manuseio de string e múltiplas palavras • Cache de intruções integrado • Cache de dados integrado

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – IBM PowerPC 450 (cont.) • 2 modos de privilégios: • Modo privilegiado (sistema operacional, drivers de baixo nível) • Modo usuário (aplicações) • 2 modos de tradução de endereço: • Modo real (acesso direto direto à memória física) • Modo virtual (tradução do virtual para o físico) • MMU (Memory Management Unit) virtual que suporta múltiplos tamanhos de páginas e uma variedade de atributos de proteção de armazenamento e opções de controle de acesso

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – IBM PowerPC 450 (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – Ethernet MAC

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – Ethernet MAC (cont.) • Virtex-4 Ethernet MAC (Media Access Control) tem 2 Ethernet MAC compartilhando uma única host interface • Suporta taxa de dados de 10/100/1000 Mb/s • Conformante com as especificações IEEE Std 802.3-2002 • Pode operar como: • Single speed Ethernet MAC a 10/100/1000 Mb/s • 3-mode Ethernet MAC • Suporta os protocolos IEEE Standard GMII e RGMII para reduzir a largura do bus para a interface física externa • Em conjunção com o RocketIO MGT fornece uma implementação completa do 1000BASE-X on-chip

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – Ethernet MAC (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – Ethernet MAC (cont.) • O bloco contem 2 Ethernet MACs compartilhando uma host interface • A host interface pode usar o generic host bus ou o DCR bus através da DVR bridge • Cada Ethernet MAC tem um filtro de endereço para aceitar ou rejeitar os frames que chegam no receive datapath • Ethernet MAC fornece vetores de estatísticas que habilitam a aquisição de estatísticas • Os vetores de estatísticas são multiplexados para reduzir o número de pinos na fronteira do bloco • Um módulo externo (StatsIP0 e/ou StatsIP1) pode ser projetado e implementado na FPGA para acumular as estatíticas do Ethernet MAC

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – Ethernet MAC (cont.)

Xilinx Virtex-4 Vinicius Funcionalidade: Virtex-4 FX – Ethernet MAC (cont.) • Lado físico • Consiste de interfaces GMII e RGMII usando I/Os padrões para acessar sinais de dado e controle de uma interface física externa • Subcamadas PCS/PMA interfaceiam diretamente o MGT • Lado cliente • Consiste das interfaces de usuário de transmissão e recepção • O módulo de controle de fluxo impede que o tráfego congestione na Ethernet MAC • A interface MDIO (Management Data I/O) permite o acesso aos registradores de controle e status na interface externa física ou à subcamada PCS quando configurado no modo 1000BASE-X e SGMII • O módulo de gerenciamento de clock configura as saídas de clocks para a freqüência correta baseando-se na velocidade interna do EMAC (10/100/1000) e no modo do EMAC (GMII, MII, RGMII, SGMII e 1000BASE-X)

Xilinx Virtex-4 Vinicius Referências Bibliográficas • Virtex-4 Family Overviewhttp://direct.xilinx.com/bvdocs/publications/ds112.pdf acessado em 30/03/2006 • Virtex-4 User Guidehttp://direct.xilinx.com/bvdocs/userguides/ug070.pdf acessado em 30/03/2006 • PowerPC 405 Processor Block Reference Guidehttp://direct.xilinx.com/bvdocs/userguides/ug018.pdf acessado em 30/03/2006 • XtremeDSP for Virtex-4 FPGAs User Guidehttp://direct.xilinx.com/bvdocs/userguides/ug073.pdf acessado em 30/03/2006 • Virtex-4 Embedded Tri-Mode Ethernet MAC User Guidehttp://direct.xilinx.com/bvdocs/userguides/ug074.pdf acessado em 30/03/2006 • Virtex-4 RocketIO Multi-Gigabit Transceiver User Guidehttp://direct.xilinx.com/bvdocs/userguides/ug076.pdf acessado em 30/03/2006

Xilinx Virtex-4 Obrigado!! Vinícius José Latorre viniciusjl@gmail.com Xilinx Virtex-4 Vinicius