Xilinx 6.3 Tutorial

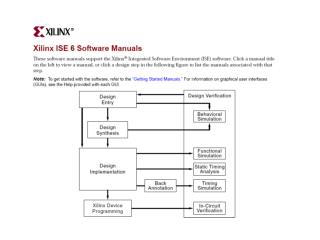

Xilinx 6.3 Tutorial. Integrated Software Environment (ISE) Set up basic environment. Select Gates or Modules to Be simulated (Insert Program Code). Run Waveform Simulation (Timing Simulation Behavioral Simulation). Xilinx 6.3 Tutorial.

Xilinx 6.3 Tutorial

E N D

Presentation Transcript

Xilinx 6.3 Tutorial Integrated Software Environment (ISE) Set up basic environment Select Gates or Modules to Be simulated (Insert Program Code) Run Waveform Simulation (Timing Simulation Behavioral Simulation)

Xilinx 6.3 Tutorial • This example will create a 4-bit counter module using a top-level schematic as a block editor. • This design contains HDL (Hardware Description Language) counter modules created with examples from the templates. • 1) Create a new project and counter module • 2) Modify the counter module (ISE tutorial in Documentation) • 2B) Modify the AND Module

Xilinx 6.3 Integrated Software Environment (ISE) • Start Programs Xilinx ISE 6.x Project Navigator • Select File New Project 1) First Screen 3) Enter Tutorial in the Project Name field, the location will be automatically entered 4) Select Schematic from the Top Level Dropdown 5) ( hit Next )

Xilinx 6.3 Tutorial 6) In the New Project Design Flow Dialog box fill in the following - Device Family: Virtex - Device: xcv50 -Package: bg256 -Speed Grade: -6 -Synthesis Tool: XST (VHDL/Verilog) -Simulator: Modelsim or Other -Generated Simulation Language VHDL 7) then Next

Xilinx 6.3 Tutorial 8) Create a VHDL module for a counter Select New Source 9) Select VHDL Module 10) Type in the file name counter 11) Make sure the “Add to project” is checked 12) Select Next

Xilinx 6.3 Tutorial 13) Select Next ( we will initially use predefined ports used in the template )

Xilinx 6.3 Tutorial 14) Select Finish

Xilinx 6.3 Tutorial 15) Select Next in the new source dialog box

Xilinx 6.3 Tutorial 16) Select next in the add existing sources box

Xilinx 6.3 Tutorial 17) Select finish in the summary dialog box

ISE creates and displays the new project and opens the counter.vhdfile in the editor

Xilinx 6.3 Tutorial (Part 2) Insert the port declarations, and the behavioral code for the VHDL counter from the ISE language templates • Open the language templates by selecting Edit Language templates • (or selecting the shortcut light bulb )

Xilinx 6.3 Tutorial (Part 2) 2) - Select VHDL

Xilinx 6.3 Tutorial (Part 2) 2) - Select VHDL - Select Synthesis Constructs

Xilinx 6.3 Tutorial (Part 2) 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions or Coding Examples (different versions of the software)

Xilinx 6.3 Tutorial (Part 2) AND Gate 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions - Select Basic Gates

Xilinx 6.3 Tutorial (Part 2) AND Gate 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions - Select Basic Gates - Select AND Gates

Xilinx 6.3 Tutorial (Part 2) AND Gate 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions - Select Basic Gates - Select AND Gates - Select 2-Input Code for AND gate Can cut and paste into program between Begin End

Xilinx 6.3 Tutorial (Part 2) AND Gate 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions - Select Basic Gates - Select AND Gates - Select 2-Input Or right click on and gate and choose option use in program Option appears insert into program. Be sure the cursor is pointing to the right part of your program

Xilinx 6.3 Tutorial (Part 2) AND Gate AND gate Code

Xilinx 6.3 Tutorial (Part 2) AND Gate Manually insert Port statements

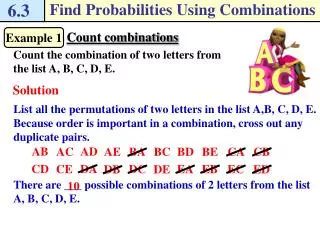

Xilinx 6.3 Tutorial (Part 2) Counter Example 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions - Select counter

Xilinx 6.3 Tutorial (Part 2) Counter Example 2) - Select VHDL - Select Synthesis Constructs - Select Common Functions - Select counter - Select 4-Bit Copy and paste code

Xilinx 6.3 Tutorial (Part 2) Counter Example The counter.vhd should look like this Code pasted

Xilinx 6.3 Tutorial (Part 2) Counter Example The counter.vhd should look like this Port code manually type in, or paste from comment code 0 )

Xilinx 6.3 Tutorial (Part 3) Creating a test Bench Waveform Source 1) Select the counter.vhd in the sources project window 2) Select Project new source

Xilinx 6.3 Tutorial (Part 3) 3) In the new source dialog box select Test Bench Waveform 4) Type in the name counter_tbw 5) Select Next

Xilinx 6.3 Tutorial (Part 3) 6) Click Next (you could associate you test bench with other sources) 7) Click Finish

Xilinx 6.3 Tutorial (Part 3) AND Gate Output Waveform for AND Gate

Xilinx 6.3 Tutorial (Part 3) Output Waveform of circuit Counter.