Large Scale Integrated Circuits

Large Scale Integrated Circuits. A Little History. In 1942, in the University of Pennsylvania's Moore School of Engineering, John Mauchly and J Presper Eckert built a machine to compute artillery firing tables for the Amercian government. . A Little History.

Large Scale Integrated Circuits

E N D

Presentation Transcript

A Little History • In 1942, in the University of Pennsylvania's Moore School of Engineering, John Mauchly and J Presper Eckert built a machine to compute artillery firing tables for the Amercian government.

A Little History • This device weighing 30 tons and containing 100,000 electronic components, including 17,000 vacuum tubes, was called the Electronic Numerical Integrator and Computer (ENIAC). • This machine was 80 feet long and 18 feet high and utilized the decimal numbering system. Mauchly and Eckert also claimed that ENIAC was the first general-purpose electronic digital computer, but in 1973 this matter was settled by a US court, which declared that the Atanasoff-Berry computer was entitled to that honor.

A Little History • Improvements continued until 1959, when both Jack Kilby, at Texas Insturments, and Robert Noyce, at Fairchild Semiconductor, discovered that resistors, capacitors and transistors could be made from a semiconductor material and that vast numbers of transistors could be etched onto a single silicon chip. • Thus, the age of integrated circuits had arrived, and from this point forward, computers continuously decreased in size and increased in power and performance.

Transistor - a tiny electrically operated switch, or gate, that can alternate between “on” and “off” many millions of times per second Microchips, Miniaturization, &MobilityFrom Vacuum Tubes to Transistors to Microchips 1940s vacuum tube towering over 1950s transistor

Transistors • Replaced vacuum tubes • Smaller • Cheaper • Less heat dissipation • Solid State device • Made from Silicon (Sand) • Invented 1947 at Bell Labs

Transistor Based Computers • Second generation machines • NCR & RCA produced small transistor machines • IBM 7000 • DEC - 1957 • Produced PDP-1

Microelectronics • Literally - “small electronics” • A computer is made up of gates, memory cells and interconnections • These can be manufactured on a semiconductor • e.g. silicon wafer

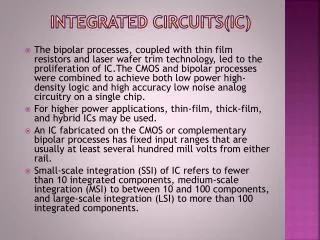

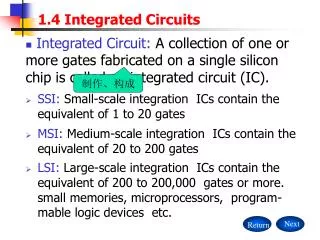

Generations of Computer • Vacuum tube - 1946-1957 • Transistor - 1958-1964 • Small scale integration - 1965 • Up to 100 devices on a chip • Medium scale integration - to 1971 • 100-3,000 devices on a chip • Large scale integration - 1971-1977 • 3,000 - 100,000 devices on a chip • Very large scale integration - 1978 to date • 100,000 - 100,000,000 devices on a chip • Ultra large scale integration • Over 100,000,000 devices on a chip

Dr. Jay W. Forrester • 1946-1951 Dr. Forrester was director of MIT's Digital Computer Laboratory and was responsible for the design and construction of Whirlwind I, the first large scale, high-speed digital computer to go into complete operation. While working on computer technology, Dr. Forrester invented random-access, coincident-current magnetic storage, which was for many years the standard memory device for digital computers. This invention , which is called magnetic core memory, involved the phenomenon that when current flows through a core, the core becomes magnetized even the current is removed. The introduction of this kind of memory makes computers smaller in size, faster to access data, and more powerful. It also was what today's memory technology was based on.

RAM • In 1970, the newly formed Intel company publicly released the 1103, the first DRAM (Dynamic Random Access Memory) chip (1K bit PMOS dynamic RAM ICs), and by 1972 it was the best selling semiconductor memory chip in the world, defeating magnetic core type memory. The first commercially available computer using the 1103 was the HP 9800 series.

RAM • Dr. Robert H. Dennard, a Fellow at the IBM Thomas J. Watson Research Center created the one-transistor DRAM in 1966. Dennard and his team were working on early field-effect transistors and integrated circuits, and his attention to memory chips came from seeing another team's research with thin-flim magnetic memory. Dennard claims he went home and within a few hours had gotten the basic ideas for the creation of DRAM. He worked on his ideas for a simpler memory cell that used only a single transistor and a small capacitor. IBM and Dennard were granted a patent for DRAM in 1968.

RAM • RAM stands for random access memory, memory that can be accessed or written to randomly -- any byte or piece of memory can be used without accessing the other bytes or pieces of memory. There were two basic types of RAM, dynamic RAM (DRAM) and static RAM (SRAM). DRAM needs to be refreshed thousands of times per second. SRAM does not need to be refreshed, which makes it faster. Both types of RAM are volatile -- they lose their contents when the power is turned off. In 1970, Fairchild Corporation invented the first 256-k SRAM chip. Recently, several new types of RAM chips have been designed.

RAM Basics • Similar to a microprocessor, a memory chip is an integrated circuit (IC) made of millions of transistors and capacitors. In the most common form of computer memory, dynamic random access memory (DRAM), a transistor and a capacitor are paired to create a memory cell, which represents a single bit of data. • The capacitor holds the bit of information -- a 0 or a 1 (see How Bits and Bytes Work for information on bits). The transistor acts as a switch that lets the control circuitry on the memory chip read the capacitor or change its state.

RAM Basics Con’t • A capacitor is like a small bucket that is able to store electrons. To store a 1 in the memory cell, the bucket is filled with electrons. To store a 0, it is emptied. The problem with the capacitor's bucket is that it has a leak. In a matter of a few milliseconds a full bucket becomes empty. • Therefore, for dynamic memory to work, either the CPU or the memory controller has to come along and recharge all of the capacitors holding a 1 before they discharge. To do this, the memory controller reads the memory and then writes it right back. This refresh operation happens automatically thousands of times per second.

Memory Modules • Memory chips in desktop computers originally used a pin configuration called dual inline package (DIP). This pin configuration could be soldered into holes on the computer's motherboard or plugged into a socket that was soldered on the motherboard. This method worked fine when computers typically operated on a couple of megabytes or less of RAM, but as the need for memory grew, the number of chips needing space on the motherboard increased.

Memory Modules Con’t • The solution was to place the memory chips, along with all of the support components, on a separate printed circuit board (PCB) that could then be plugged into a special connector (memory bank) on the motherboard.

Moore’s Law • Gordon Moore made his famous observation in 1965, just four years after the first planar integrated circuit was discovered. The press called it "Moore's Law" and the name has stuck. In his original paper, Moore observed an exponential growth in the number of transistors per integrated circuit and predicted that this trend would continue. Through Intel's relentless technology advances, Moore's Law, the doubling of transistors every couple of years, has been maintained, and still holds true today. Intel expects that it will continue at least through the end of this decade.

Moore’s Law • Increased density of components on chip • Gordon Moore - cofounder of Intel • Number of transistors on a chip will double every year • Since 1970’s development has slowed a little • Number of transistors doubles every 18 months • Cost of a chip has remained almost unchanged • Higher packing density means shorter electrical paths, giving higher performance • Smaller size gives increased flexibility • Reduced power and cooling requirements • Fewer interconnections increases reliability

Steps in Manufacture of a Microchip • Make large drawing. Reduce drawing hundreds of times to microscopic size. • Duplicate reduced photo many times on sheet.

Steps in Manufacture of a Microchip • Print sheet of multiple copies on a wafer made of silicon, a semiconductor. • Print layer after layer above and below original silicon surface.

Steps in Manufacture of a Microchip • Cut wafer into chips. • Mount chip in frame with connective pins extruding.

Miniaturization Miracles: Microchips, Microprocessors, & Micromachines • Types of microchips: • Memory • Logic • Communications • Graphics • Math • Microprocessor • Microcontroller

Overview of Wafer Fabrication • Four stages of Semiconductor Manufacturing • material prep • crystal growth and wafer prep • wafer fabrication • packaging • Wafer Fabrication • the series of processes used to create the semiconductor devices in/on the surface of the wafer

Wafer Terminology • Chip, die, microcircuit, die,bar • the identical circuits covering the wafer • Scribe lines, saw lines, streets, avenues • small areas between the chips used to separate them • Engineering die, test die • special devices or circuits containing special chemicals to be tested during processing • Edge die • partial die patterns that will not function

Wafer Terminology (cont.) • Wafer crystal plane • the crystal structure toward which the chip edges are oriented • Wafer Flats • the flatted edge which indicates the crystal structure and material type

Basic Wafer Fab Operations • Layering • Patterning • Doping • Heat Treatments

Layering • Adding thin layers to the wafer surface • either insulators, conductors or semiconductors • deposited by two major techniques - growing or deposition • Oxidation - growing a silicon dioxide layer on the wafer surface • Deposition - common techniques are CVD (chemical vapor deposition) Evaporation and Sputtering.

Patterning • Series of steps resulting in removal of certain portions of the added surface layers • After removal a patternof the layeris left on the wafer surface. • Material removed may be in the form of a whole or just an island of material. • Patterning process known by names Litho, Masking, Photolithography, Photomasking, Microlithography • Patterning is the most critical basic operation.

Patterning (cont) • Goal is to: • create circuit parts in the exact dimensions (feature size) required by the circuit design • locate them in their precise location on the wafer surface. • Errors in process or placement can change the electrical functions of the device. • Contamination can introduce serious defects that result in loss of good die.

Doping • Places specific amounts of dopant in the wafer surface through openings in the surface layer. • Two techniques used are Ion Implantation and Thermal Diffusion. • Thermal diffusion - chemical process that takes place when wafer is heated to about 1000° C and exposed to vapors of the proper dopant. • Ion Implantation - physical process in which dopant atoms are ionized, accelerated to high speed and “shot” into the wafer surface

Doping (cont) • Purpose: • create either N type or P type pockets in the wafer surface • these pockets form the PN junctions required for operation of the transistors, capacitors, diodes and resistors in the circuit

Heat Treatment • Heat treatment to achieve specific results. • Annealing - • heat treatment (about 1000° C) occurring after ion implantation to repair disruptions in the wafer crystal structure. • Alloying - • occurs after metal conductor strips placed on wafer. Metal alloyed(about 450° C) to wafer surface to ensure good electrical conduction.

Semiconductor ManufacturingProcess Steps • Hundreds of steps are often required in the wafer processing of an I.C. • The four basic operations are used repeatedly to build the parts of the device in and on the wafer.

Building an MOS Transistor • Circuit Design • Block diagram of the circuit • Schematic • Circuit layout - using CAD of the composite (composite - the entire circuit including every layer) • The drawings are separated into layers and digitized (translating to a digital database) • Final drawing completed on a computerized X-Y plotter table

Reticles and Mask • Reticle -a “hard copy” of the individual drawing recreated in a thin layer of chrome deposited on a glass or quartz plate. • May be used directly in the photo process or used to make a photo-mask or mask. • Masks are used to pattern a whole surface in one pattern transfer. Masks and reticles are similar in makeup. • Reticles and Masks are produced in a separate department or purchased from an out side vendor. • A Mask “set”is supplied for each type of circuit.

Semiconductor Manufacturing Wafer Fabrication Overview

Wafer Fabrication Overview • Layering • Patterning • Doping • Heat Treatment

Layering Operation • Thin layers of either conductor or insulator material are added to a wafer of silicon using one of two techniques. • Grown • Oxidation • Nitradation • Deposited • Chemical Vapor Deposition • Evaporation • Sputtering

Patterning • Series of steps to remove oxide from a new layer to begin to form the circuit path. • These processes are known as Lithography, Masking or variations of those names. • The repeating of this process creates the surface parts of the device that make up the circuit. • A most critical operation - sets dimensions for device

Doping • Process whereby specific amounts of dopant are embedded in the wafer through openings in the surface layers. • Thermal Diffussion and Ion Implant are two techniques commonly used to accomplish this.

Heat treatment • Operations in which the wafer is heated and cooled to obtain two specific outcomes, “annealing” and “alloying”. • Annealing is the repair of a wafer’s crystal structure after ion implant has disrupted it. • Alloying is heat treating the wafer after metal deposition to ensure good electrical conduction.