RISC

RISC. Увод Коришћење великог броја регистара RISC архитектура Проточност код RISC архитектура. Увод. Почев од првих рачунара са запамћеним програмом (око 1950.) било је мало стварних иновација у области архитектуре и организације рачунара. Концепт фамилије.

RISC

E N D

Presentation Transcript

RISC Увод Коришћење великог броја регистара RISC архитектура Проточност код RISC архитектура

Увод • Почев од првих рачунара са запамћеним програмом (око 1950.) било је мало стварних иновација у области архитектуре и организације рачунара. • Концепт фамилије. • Микропрограмирана управљачка јединица. • Кеш меморија. • Проточност. • Вишеструки процесори.

Увод • Овој листи треба додати најинтересантнију и, могуће, најважнију иновацију: RISC (Reduced Instruction Set Computer) архитектуру. • RISC архитектура представља драматично скретање од историјских трендова. • Неке заједничке, кључне карактеристике RISC архитектура су: • Велики број регистара опште намене (32 и више) и/или употреба компилаторских технологија за оптимизацију употребе регистара. • Ограничен и једноставан скуп инструкција. • Нагласак на оптимизацији проточности инструкција.

Коришћење великог броја регистара • Пожељан је брз приступ операндима. • Велики је удео једноставних наредби доделе у програмима. • У програмима постоји значајан број приступа операндима који су у највећем броју случајева локалне скаларне вредности. • Ови разлози наводе на коришћење великог броја регистара код RISC архитектура.

Коришћење великог броја регистара • Да би се ово омогућило постоје два приступа: софтверски и хардверски. • Софтверски приступ се ослања на рад компилатора. • Хардверски приступ састоји је једноставно у коришћењу већег броја регистара како би се већи брј променљивих што дуже држао у њима.

Коришћење великог броја регистара • Већина операнада су локални скалари па је очигледан приступ њихово смештање у регистар уз неколико регистара за глобалне променљиве. • Проблем је што се дефиниција локалног мења са сваким позивом процедуре или повратком из процедуре. • При сваком позиву се локалне променљиве морају из регистара пребацити у меморију. Осим овога морају се преносити параметри. При повратку, променљиве морају поново да се напуне у регистре као и да се врати резултат позваног програма. • Решење се заснива на томе да типична процедура захтева свега неколико параметара и локалних променљивих. Осим тога, дубина позива процедура се креће у релативно уском опсегу.

Ниво J Параметарски регистри Параметарски регистри Локални регистри Локални регистри Привремени регистри Привремени регистри Call/return Ниво J+1 Сл. 1. Преклапање регистарских прозора. Коришћење великог броја регистара • Да би се ова својства искористила користе се регистарски прозори. • Прозори суседних процедура се преклапају како би се омогућио пренос параметара.

Коришћење великог броја регистара • Да би се обрадила свака могућа комбинација позива и повратака, број регистарских прозора мора да буде неограничен! • Уместо тога, регистарски прозори се користе тако да садрже неколико најскоријих активација процедура. • Старије активације морају да се запамте у меморију а обнављају се када се смањи дубина позива. • Дакле, стварна организација регистарског поља је кружни бафер са преклапајућим прозорима.

Сл. 2. Организација кружног бафера са преклапајућим прозорима. Коришћење великог броја регистара

Коришћење великог броја регистара • Шема са прозорима је ефикасна за памћење локалних скалара али не покрива памћење глобалних променљивих. • Две могућности: • Глобалним променљивама се додељују меморијске локације. • Уграђује се скуп глобалних регистара у процесор.

Коришћење великог броја регистара

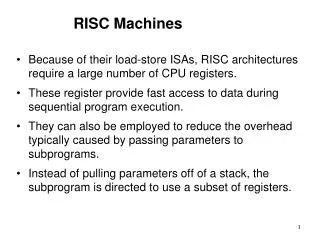

RISC архитектура • Карактеристике CISC машина • Приметан је тренд обогаћивања скупа инструкција. • Први разлог за то је да се олакша посао компилатора. • Други разлог је у побољшању перформанси, јер CISC машине дају мање и брже програме. • Међутим, компликује се управљачка јединица а програми, иако краћи по броју инструкција, могу заузимати више битова.

RISC архитектура • Карактеристике RISC машина • Једна инструкција по тактном периоду. • Операције типа регистар-регистар. • Једноставни адресни начини рада. • Једноставан формат инструкција.

Проточност код RISC архитектура • Проточност код обичних инструкција: • Већина инструкција је регистарског типа и захтева две фазе: • I : Припрема инструкције. • E : Извршење (обавља се ALUоперација са регистарским улазом и излазом). • Инструкције loadи store захтевају три фазе: • I : Припрема инструкције. • E : Извршење – израчунавају се меморијске адресе. • D : Обраћање меморији – операције регистар у меморију или меморија у регистар.

Load A M Load B M Add C A+B Store M C Branch X I I E E D D I E D I E I I E E D D I E Проточност код RISC архитектура a) б) Load A M Load B M Add C A+B Store M C Branch X NOOP I E D I E I E I E Сл. 3. Ефекти проточности. (а) Секвенцијално извршење; (б) Двостепени проточни систем.

Проточност код RISC архитектура • Два проблема спречавају постизање максималног двоструког убрзања: • Претпоставка да је могућ само једноструки приступ меморији. • Инструкција гранања ремети секвенцијални ток извршења. Да би се извршило одговарaјуће прилагођавање компилатор убацује инструкцију NOOP. • Проточност се може побољшати дозвољавањем два приступа меморији по степену (слика 4).

Load A M Load B M NOOP Add C A+B Store M C Branch X NOOP I E D I I E E D D I E I E I E I E Сл. 4. Ефекaт проточностикод тростепеног система. Проточност код RISC архитектура • Сада се три инструкције могу преклапати. • Гранање спречава максимално убрзање. • Зависности по подацима захтевају убацивање додатне NOOP операције.

Проточност код RISC архитектура • Проточни систем ће боље радити ако су фазе подједнаког трајања. Како фаза Е обухвата рад ALU она је обично дужа од осталих, па је згодно да се подели на две фазе: • Е1: Читање регистара. • Е2: Рад ALU и упис у регистар. • На слици 5 је илустрован рад четворостепеног проточног система.

I E1 E2 D Load A M Load B M NOOP Add C A+B Store M C Branch X NOOP NOOP I E1 E2 D I E1 E2 I E1 E2 I E1 E2 D E2 I E1 I E1 E2 E2 I E1 Проточност код RISC архитектура Сл. 5. Ефекaт проточностикод четворостепеног система.

Проточност код RISC архитектура • Да би се компензовале зависности по подацима и због гранања развијене су различите технике. • Закашњено гранање је техника код које гранање нема ефекта док се не изврши следећа инструкција. • Инструкција која непосредно прати инструкцију гранања назива се слот кашњења.

време 5 7 1 3 4 6 2 100 LOAD X,A 101 ADD 1,A 102 JUMP 105 103 ADD A,B 105 STORE A,Z I E D I E I E I I E D Сл. 6. Традиционална проточност. Проточност код RISC архитектура

време 5 7 1 3 4 6 2 100 LOAD X,A 101 ADD 1,A 102 JUMP 106 103 NOOP 106 STORE A,Z I E D I E I E E I I E D Сл. 7. RISC проточностса убаченим NOOP. Проточност код RISC архитектура

време 5 7 1 3 4 6 2 100 LOAD X,A 101 JUMP 105 102 ADD 1,A 105 STORE A,Z I E D I E I E I E D Сл. 8. Измењен редослед инструкција. Проточност код RISC архитектура