A Semi-Canonical Form for Sequential AIGs

380 likes | 509 Views

This paper presents a novel approach to efficiently identify isomorphic sub-circuits in sequential AIGs through a semi-canonical form. Recognizing identical sub-circuits can significantly reduce redundant computation in synthesis and verification processes. The proposed algorithm generates unique signatures for nodes and utilizes their structural attributes to categorize and relabel sub-circuits, thereby minimizing duplicate analyses. Experimental results demonstrate the effectiveness of this method in decreasing proof obligations, illustrating its applicability in advanced circuit design and verification.

A Semi-Canonical Form for Sequential AIGs

E N D

Presentation Transcript

A Semi-Canonical Form for Sequential AIGs Alan Mishchenko, Niklas Een, Robert BraytonUC Berkeley Michael Case, Pankaj Chauhan, Nikhil Sharma Calypto Design Systems

OUTLINE • Introduction • Motivation example • Background • Algorithm • Experimental results • Conclusion

INTRODUCTION • In sequential and-inverter-graphs (AIGs) there frequently exist many instances of the same logic sub-circuit but with different inputs • Many synthesis and verification packages spend significant time analyzing logic, and the presence of identical sub-circuits results in duplication of effort • Leads to redundant work • Tools re-analyze the same sub-circuit • Waste time on duplicate proof obligations • Suppose a tool is re-run on a minimally-changed netlist, do we re-analyze sub-circuits that haven’t changed?

INTRODUCTION • Key idea: identify duplicate logic regionsIdeal solution: isomorphism • An approximate solution: semi-canonical mapping • Use the circuit structure to classify each sub-circuit • Use re-labeling and listing in numerical order

MOTIVATION • PI(b) : two fanout, level 0 • Internal node (m) : two fanout, level 1 • PI(c) : one complemented edge • PO(F) : two same-level fanins • PO(G) : two different-level fanins • …

APPLICATIONS • 1. Detect structurally isomorphic primary outputs (POs) of a multi-output sequential AIG • 2. In verification, where each output represents a property to be proved, if two outputs are isomorphic then it is only necessary to solve one • When verifying a set of outputs, only one representative of each isomorphic class need be considered, reducing the number of proof obligations • 3. It can be used to cache synthesis or verification results that have been computed previously on an AIG

OUTLINE • Introduction • Motivation example • Background • Algorithm • Experimental results • Conclusion

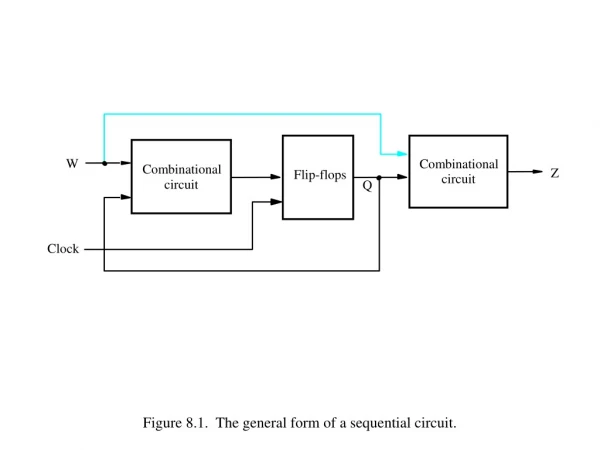

BACKGROUND • Asequential AIG has a constant node, primary inputs andoutputs, flop inputs and outputs, and internal AND nodes • Node attributes {PI, PO, FF, internal} • Edgeattributes {direction, complementation} • Two graphs areidentical ( H ≡ G ) if their representations are identical • The conventional representation of an AIG is asequence of triplets {(a1,b1,c1),…,(aN,bN,cN)}

BACKGROUND • An isomorphism f between two attributed graphs, H and G, is a 1-1 mapping f: V(G) → V(H), where nodes (u, f (u) ) have the same attributes, and edges (u →v, f (u)→ f (v)) have the same attributes • Two graphs are isomorphic (G ≈ H ) if an isomorphism exists between the two

BACKGROUND • Graph canonization is the problem of finding a mapping canon: V(G) → V(G) such that • 1. canon(G) ≈ G , and • 2. [ canon(H) ≡ canon(G) ]⇔[ H ≈ G ] • canon(G) is said to be a canonical form for G and canon is said to be a canonical mapping for G.

DISCUSSION • Semi-canonical mapping • We give an algorithm for re-labeling of nodes of V(G), iso, such that iso(G) ≈ G • Clearly if iso(H) ≡ iso(G) , then H ≈ G • We do not claim that iso is a canonical mapping, but we do claim that for the majority of graphs if H ≈ G , then iso(H) ≡ iso(G)

OUTLINE • Introduction • Motivation example • Background • Algorithm • Experimental results • Conclusion

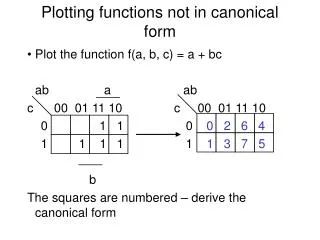

Our Approach • Signature: a value reflecting the circuit structure surrounding a node • Goal: assign unique signatures to all nodes • Semi-canonical form: represent an AIG on disk by ordering nodes by topological order & signatures 42 71 15 19 2 3 4 1

ALGORITHM • Computing semi-canonical labels • Computing edge values • Node signature propagation • Refining node signature • Breaking ties

Algorithm • Compute signatures for each node • Goal: assign unique signatures to all nodes • Initially all signatures are 0 0 0 0 0 0 0 0 0

Algorithm • Edge value: reflects the structure around an edge

Algorithm • Edge value: reflects the structure around an edge 3 3 1 1 1 2 1

Algorithm • Function: PropagateSignaturesForward() • Assign the same random signature to all inputs • Note: deterministic random numbers are used 3 3 3 1 1 1 2 1 12 12 12 12

Algorithm • Function: PropagateSignaturesForward() • Node signature is computed as the sum of (a) its old • signature, (b) its node-fanin signatures, and (c) its fanin edge values 59 43 3 3 3 1 27 1 26 1 2 1 12 12 12 12

Algorithm • Function: PropagateSignaturesForward() • Node signature is computed as the sum of (a) its old • signature, (b) its node-fanin signatures, and (c) its fanin edge values 59 LB1 43 LB2 3 3 3 1 LB3 27 LB4 1 26 1 2 1 12 12 12 12

Algorithm • Function: PropagateSignaturesBackward() • (Recompute edge values) • Starting signatures for primary inputs are not assigned and signatures of the POs are not changed • The AIG is traversed in the reverse topological order • Instead of fanins and fanin edges, fanouts and fanout edges are considered; • Signatures are transferred from flop outputs to flop inputs and not vice versa.

Refining node signatures • Refining node signatures • Refinement refers to the process of updating signatures for every node to reduce the number of nodes having the same signature

Refining node signatures • Starting signatures for primary inputs are not assigned and signatures of the POs are not changed 59 LB1 43 LB2 3 3 3 1 LB3 27 LB4 1 26 1 2 1

Refining node signatures • Starting signatures for primary inputs are not assigned and signatures of the POs are not changed 59 LB1 43 LB2 3 3 3 1 LB3 27 LB4 1 26 1 2 1

Refining node signatures 59 43 3 3 3 1 135 1 88 1 2 1

Refining node signatures 59 43 3 3 3 1 135 1 88 1 2 1 89 225 137 44

Refining node signatures LB1 LB2 59 43 LB3 3 3 3 LB4 1 135 1 88 1 2 1 89 225 137 44 LB5 LB6 LB7 LB8

Breaking ties • Sometimes we cannot distinguish nodes tie breaking • Choose the equiv class with the largest level • Assign unique signatures to the class nodes • Propagate signatures to other nodes until convergence • If there some equiv classes are left, go to Step 1 71 42 15 15

Breaking ties • Sometimes we cannot distinguish nodes tie breaking

OUTLINE • Introduction • Motivation example • Background • Algorithm • Experimental results • Conclusion

Implementation • Implemented within ABC as an internal routine • Puts the netlist in semi-canonical form • Node order reflects both topological order & signatures • Creating the semi-canonical AIGER file and checking isomorphism : “write_aiger –u” • Filtering isomorphic POs: “&iso”

Implementation • Creating the semi-canonical AIGER file and checking isomorphism • Writes the netlist in semi-canonical form • Sort the nodes in the order of their new labels along with their fanins ordered according to increasing fanin node label • Normalizes the netlist, allows for caching of results Netlist N write_aiger -u N.aig diff Netlist N’ write_aiger -u Nprime.aig

Implementation • Filtering isomorphic POs • Multi-output netlist series of single output netlists • Put each netlist into semi-canonical form • Discard isomorphic POs F’ G’ b’ c’ d’ a' • Isomorphisms: F ≈ F’ , G ≈ G’ • Counterexamples/invariants on F/G can be re-mapped to F’/G’

EXPERIMENTALRESULTS • Publicbenchmarks

EXPERIMENTALRESULTS • Industrial benchmarks

Conclusion • Previous work: • computing functional symmetries and automorphisms • simplifying reachability and SAT instances with symmetries • First work on semi-canonical labeling of nodes in a sequential AIG • Allows for detecting duplicate circuits in EDA tools • Future work may include: • Speeding up propagation of node signatures • Generalizing the algorithm to work for logic networks other than the traditional AIGs